Lecture 8.2 | The Processor-Part2

:material-circle-edit-outline: 约 427 个字 :fontawesome-solid-code: 8 行代码 :material-clock-time-two-outline: 预计阅读时间 2 分钟

承接上节课的预测

期中考试考到单周期,流水线不考

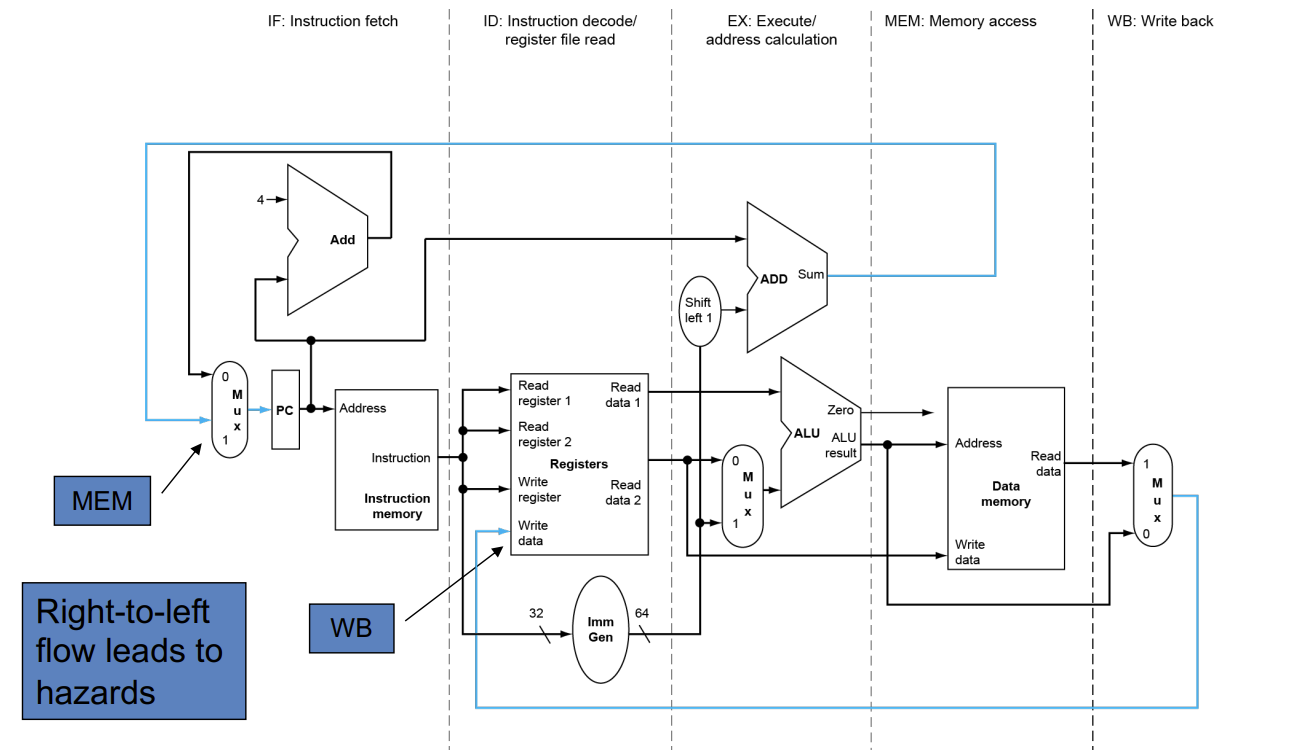

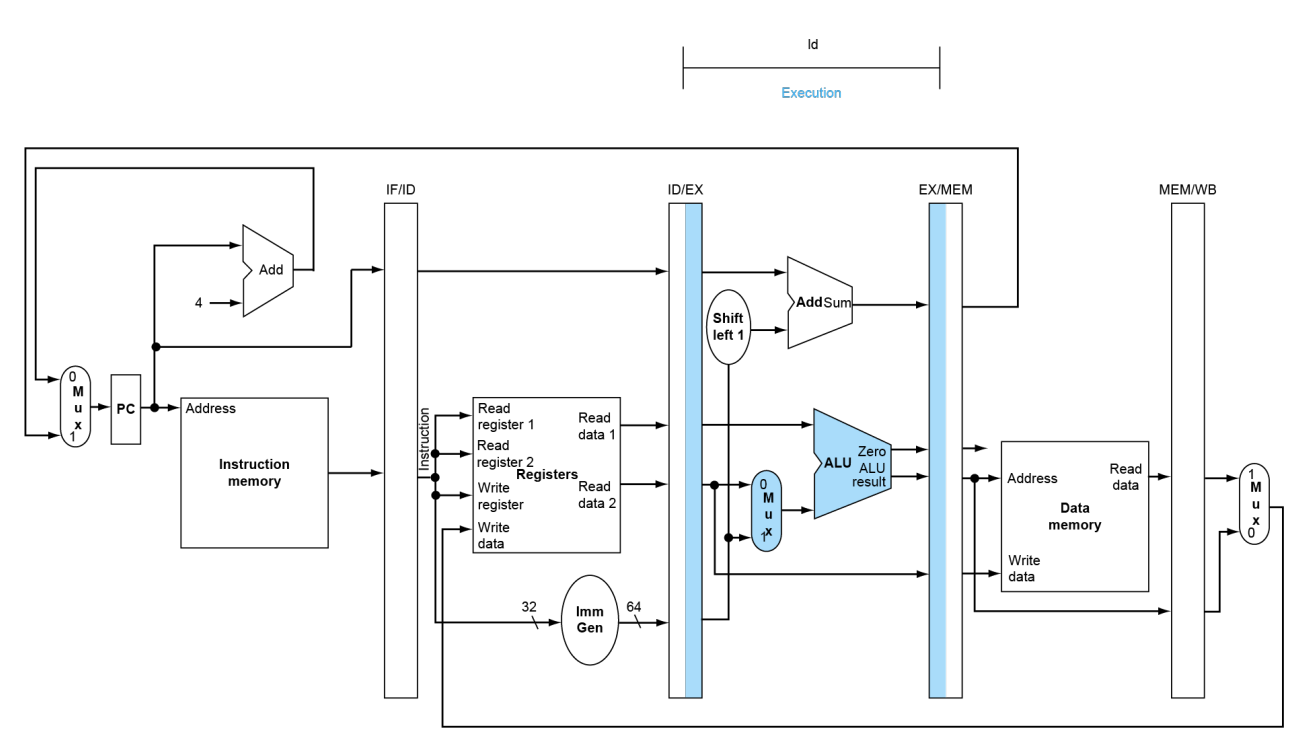

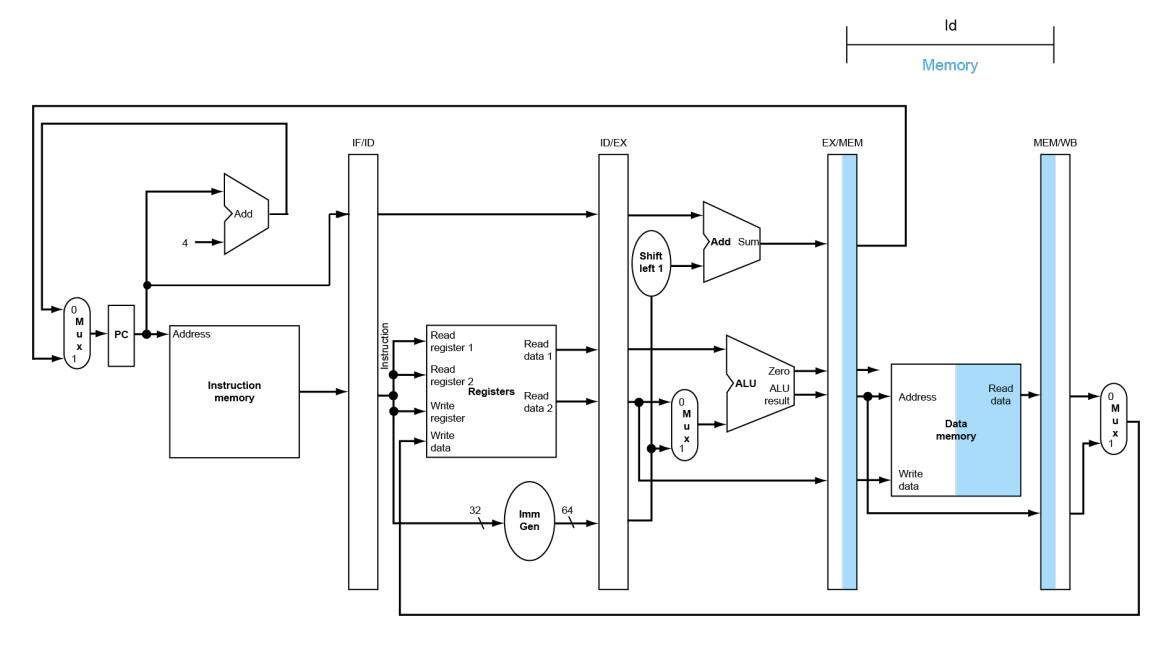

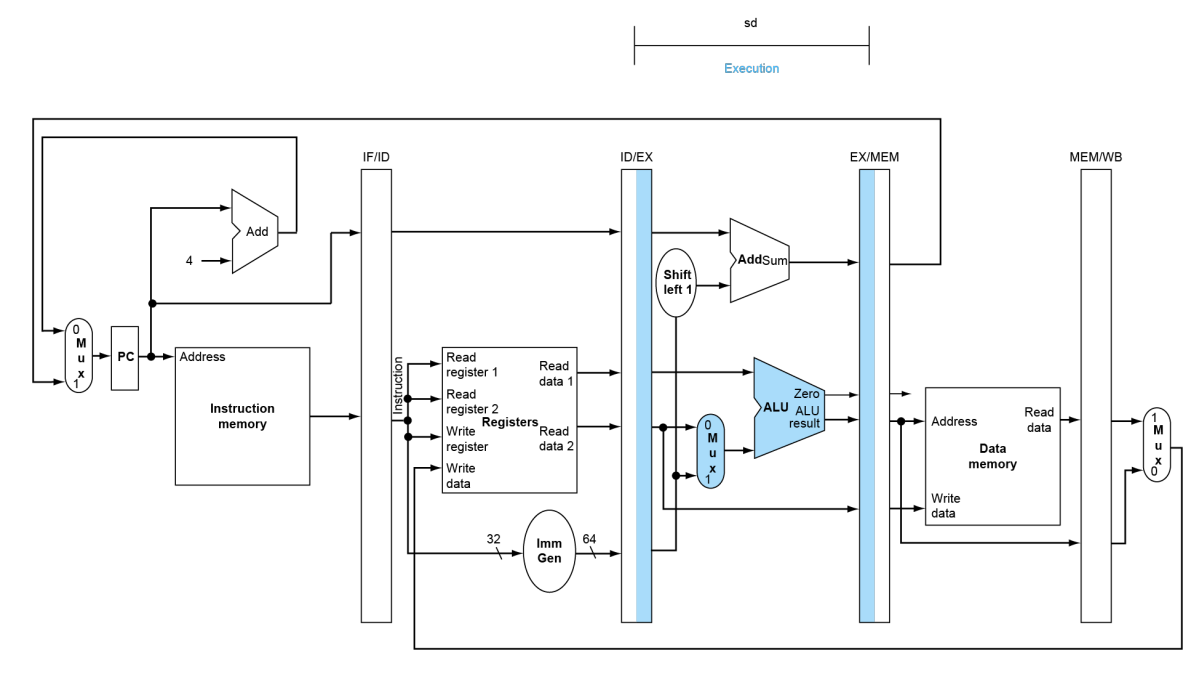

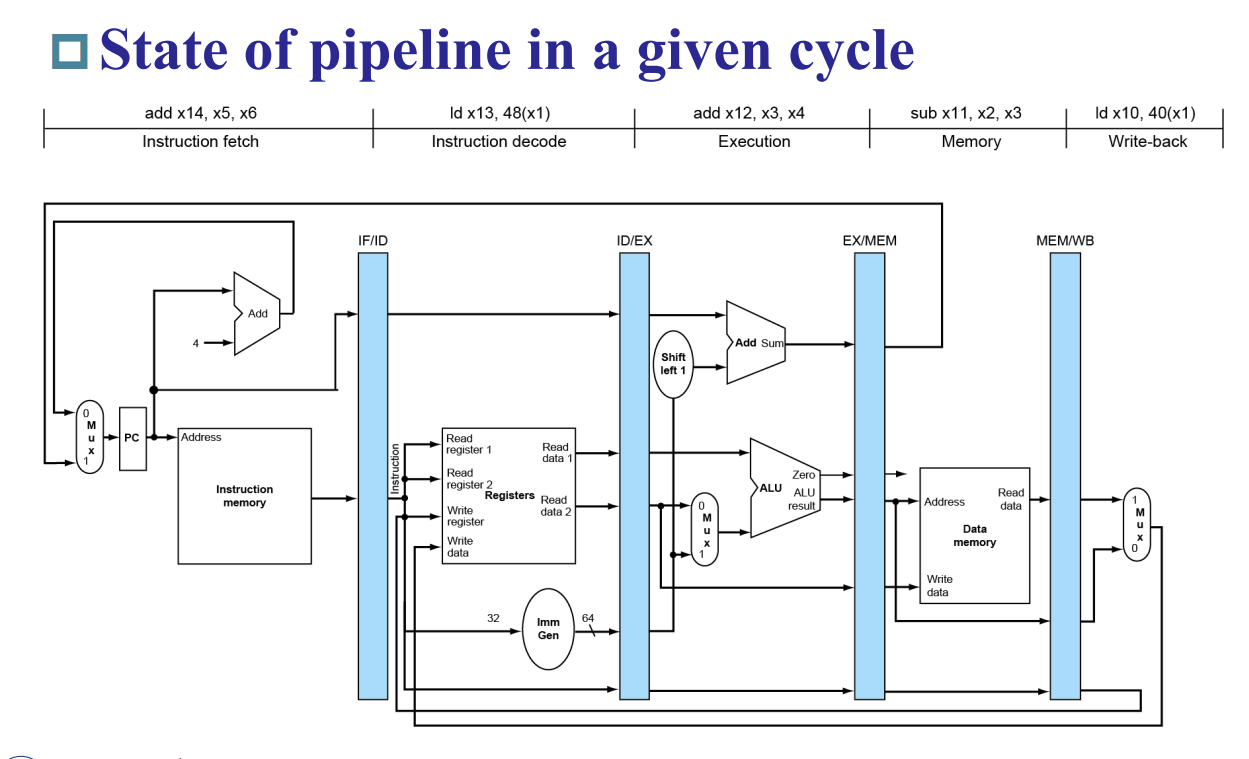

4.6 RISC-V Pipelined Datapath

单周期图划为五个区域,对应流水线的五个阶段

当然这不是最终的版本

从右往左的线会造成hazard

左上角对应了控制冒险,这个mux决定下一条指令是pc+4还是跳转到imm对应的地址

右下角对应了数据冒险

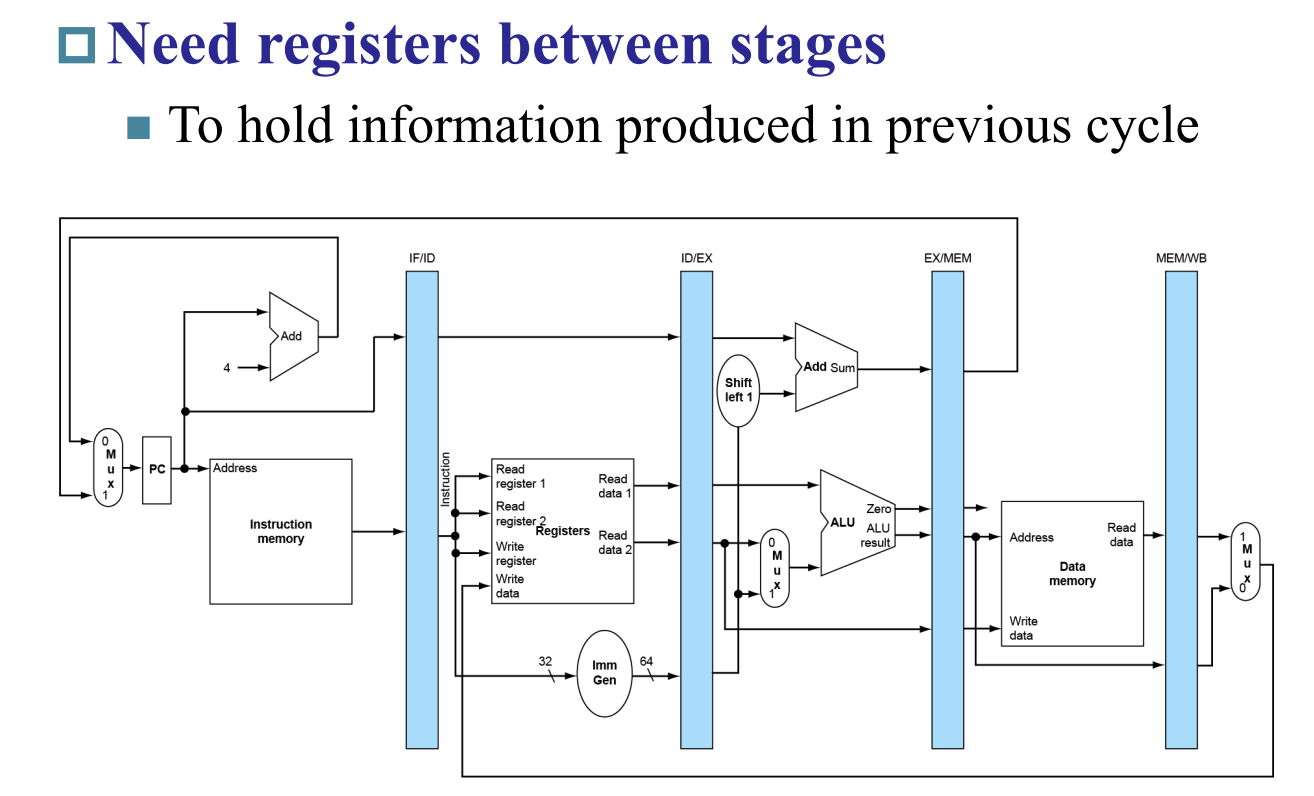

Pipeline registers

通过阶段之间的reg储存上一阶段的结果,方便下一阶段使用

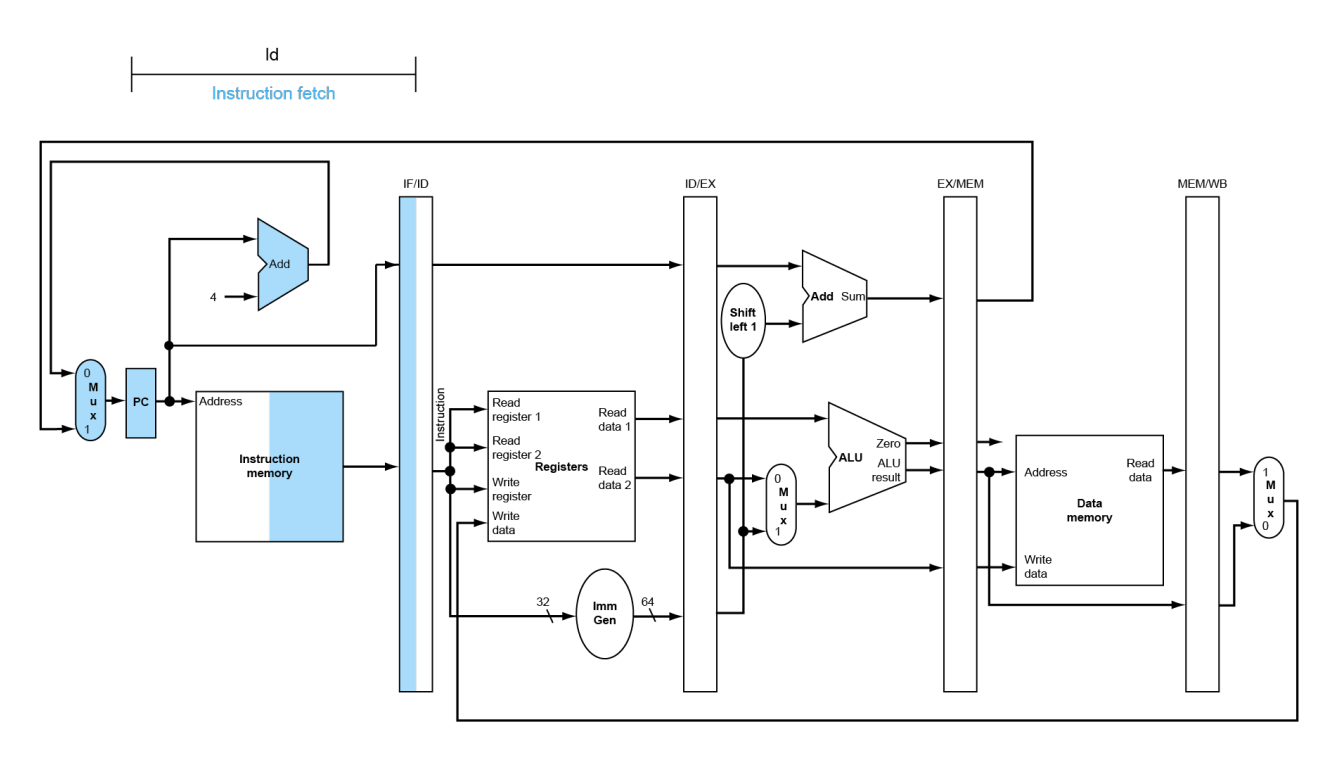

IF for Load, Store, …

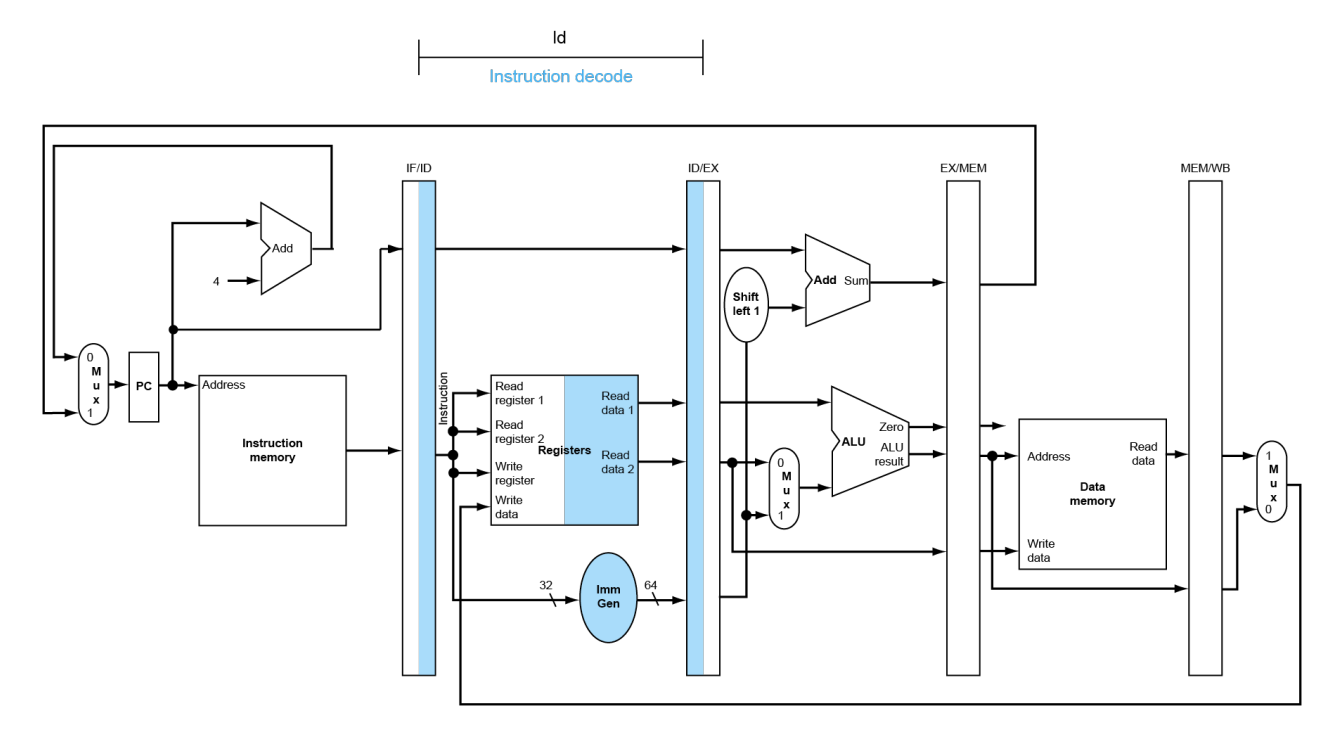

ID for Load, Store, …

EX for Load

MEM for Load

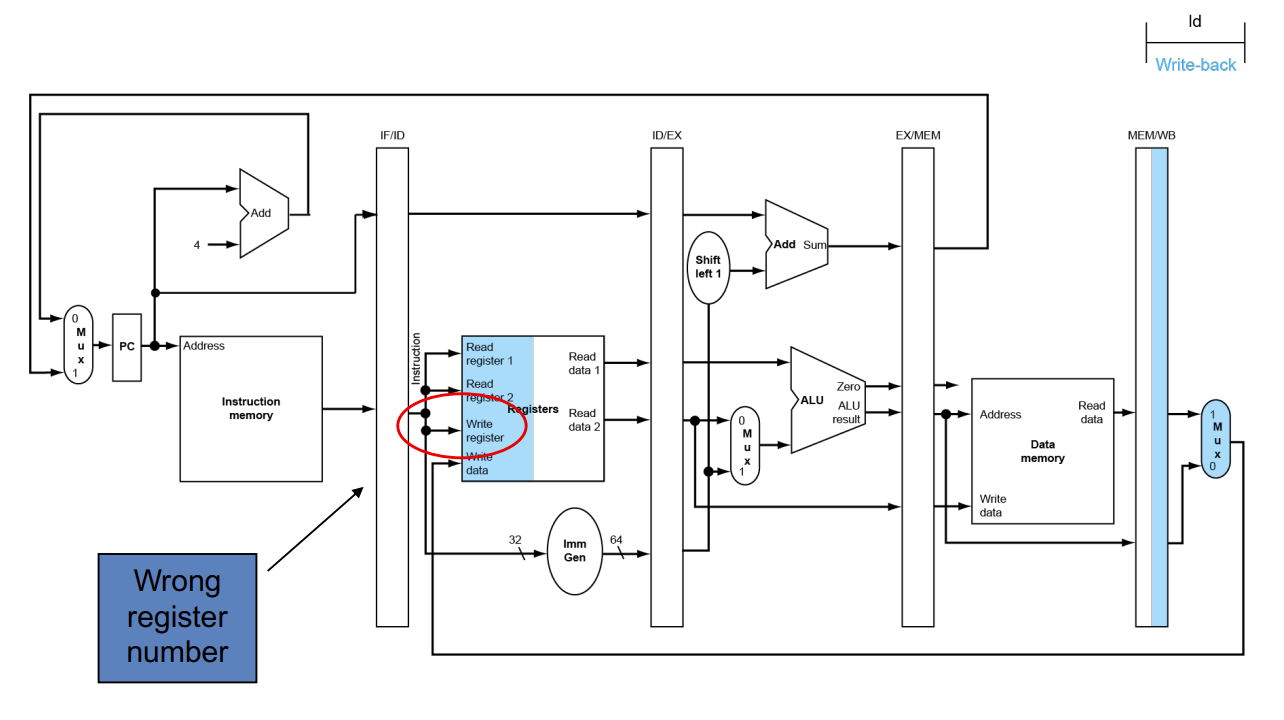

WB for Load

这张图有问题,地址是不对的

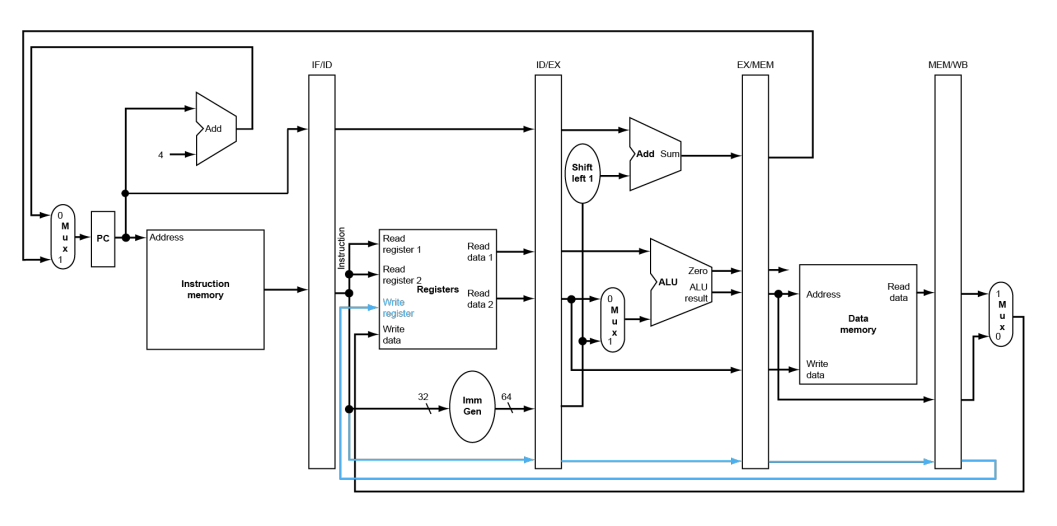

Corrected Datapath for Load

EX for Store

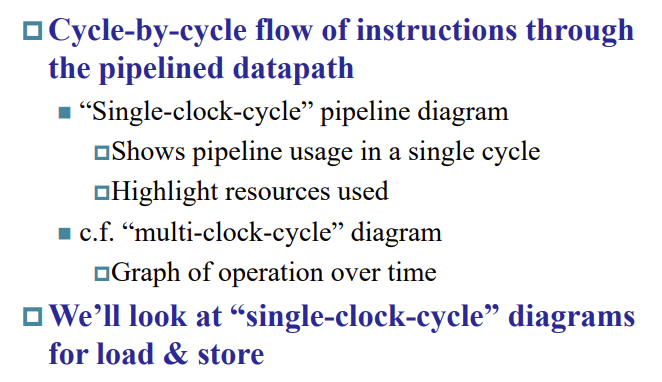

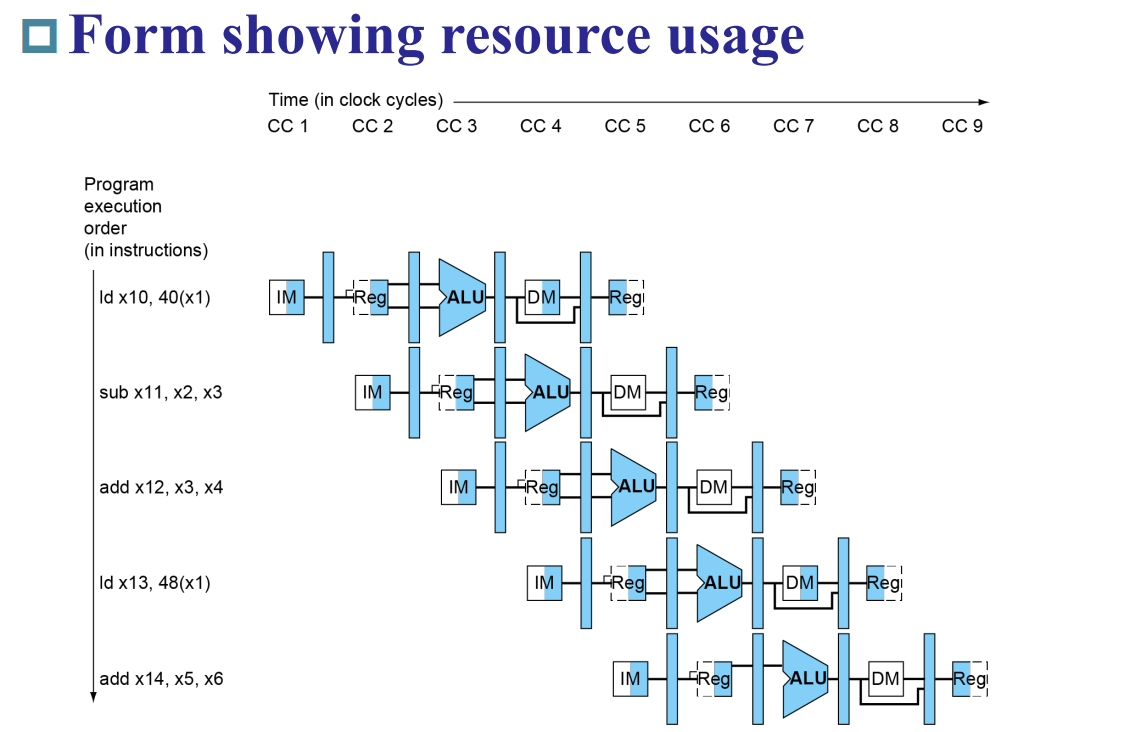

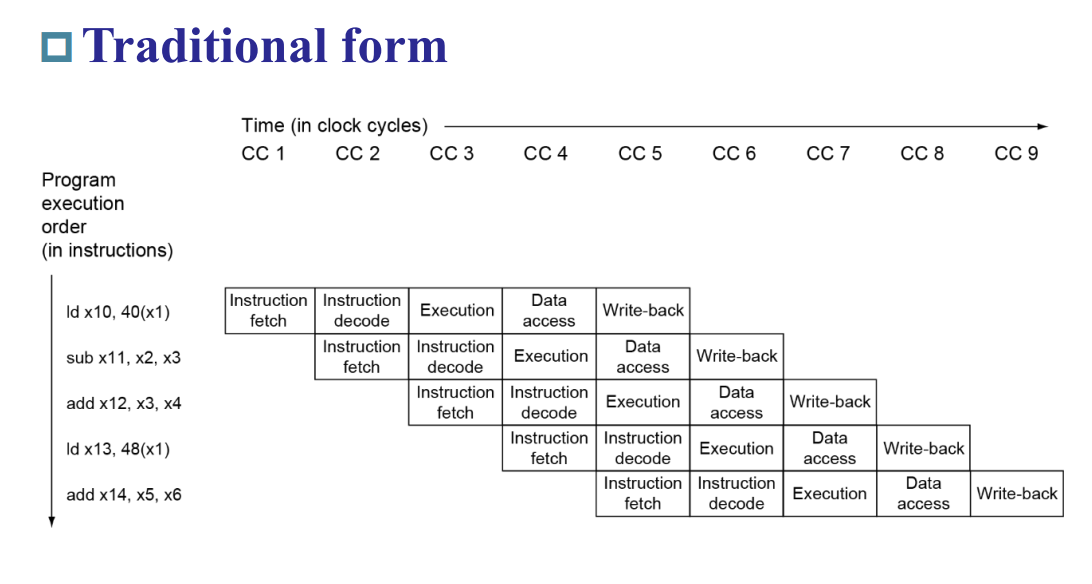

Pipeline Operation

注意记一下两种diagram的名字

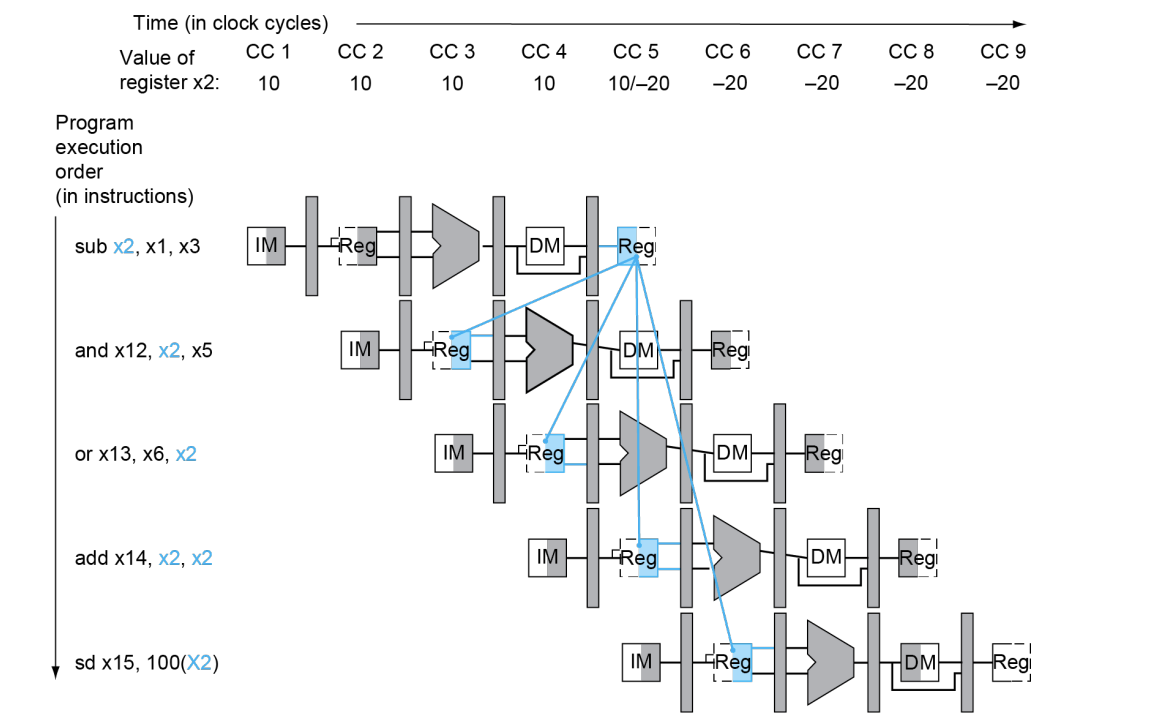

Multi-Cycle Pipeline Diagram

下图为简化画法,考试就用这种画就行

Single-Cycle Pipeline Diagram

指令放最上面

注意是与muti-cycle相反,最上面这一行指令是从右往左顺序,即先运行

ld x10, 40(x1)

Pipelined Control

都要背下来

Pipelined Control (Simplified)

没有考虑jal,不然太复杂了

4.7 Data Hazards

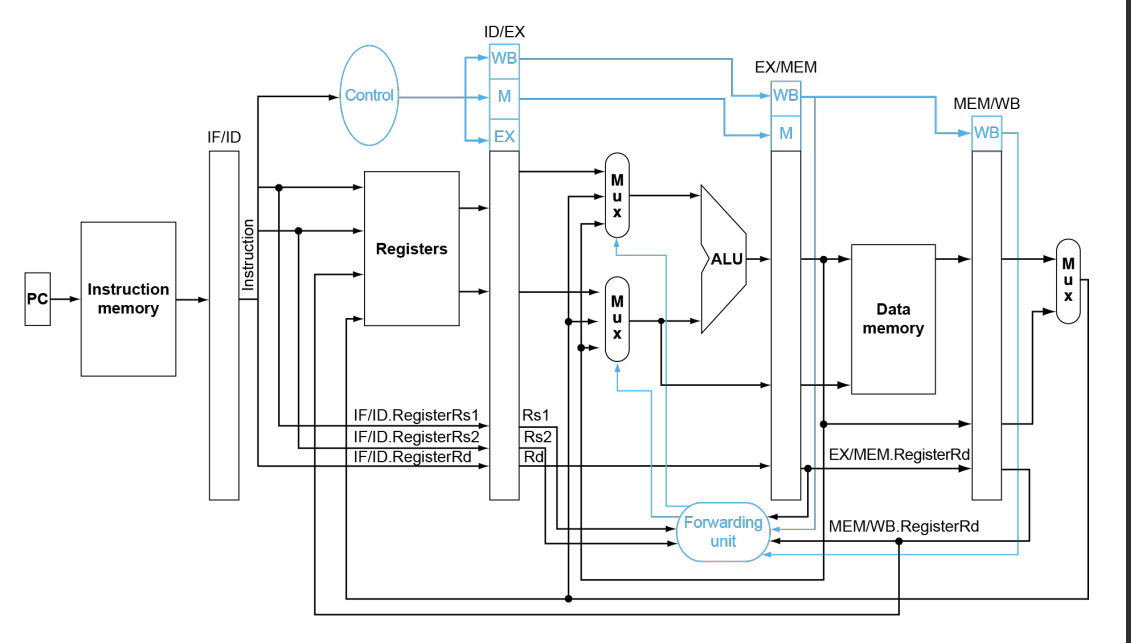

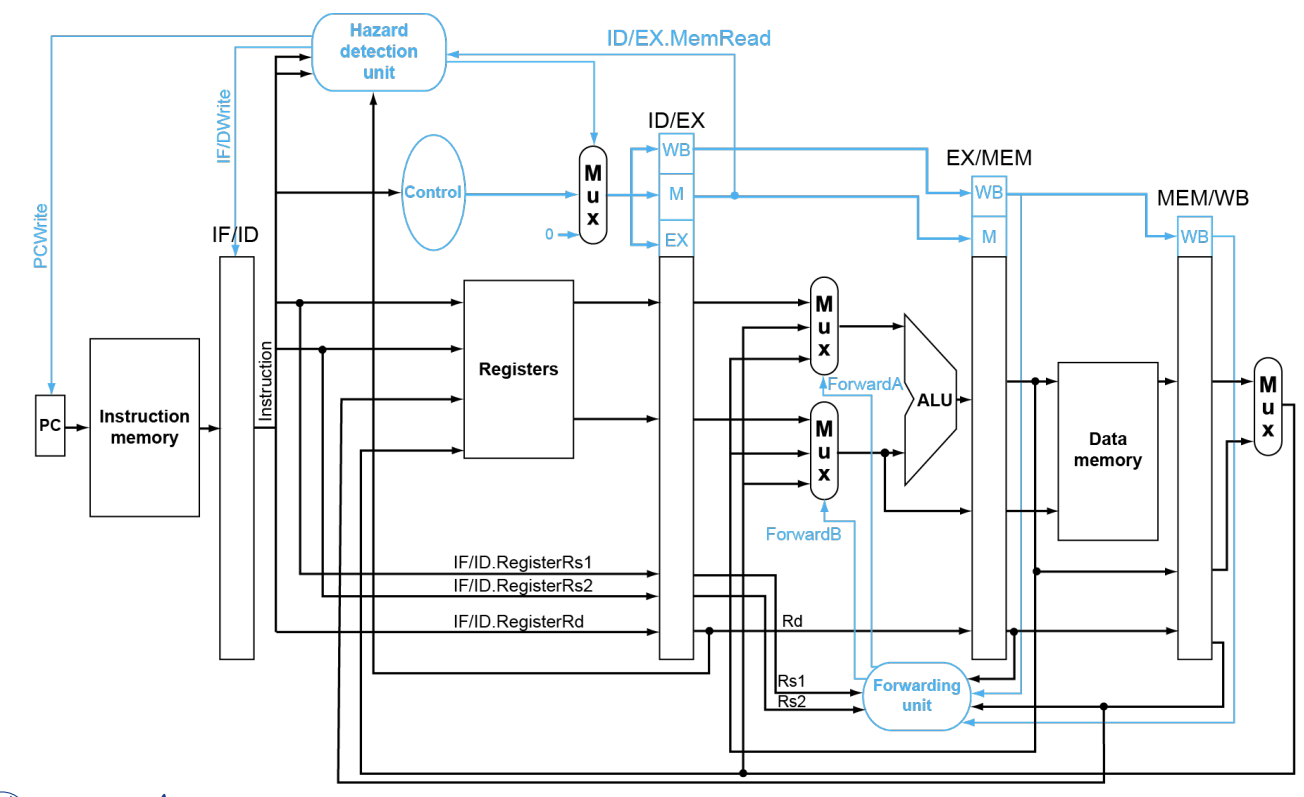

如何去解决data hazard,如何实现forwarding

Consider this sequence:

Dependencies & Forwarding

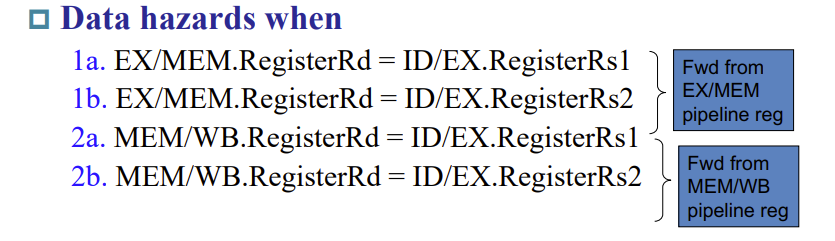

Detecting the Need to Forward

- Pass register numbers along pipeline

- e.g., ID/EX.RegisterRs1 = register number for Rs1 sitting in ID/EX pipeline register

- ALU operand register numbers in EX stage are given by

- ID/EX.RegisterRs1, ID/EX.RegisterRs2

- But only if forwarding instruction will write to a register!

- EX/MEM.RegWrite, MEM/WB.RegWrite

- And only if Rd for that instruction is not x0

- EX/MEM.RegisterRd ≠ 0, MEM/WB.RegisterRd ≠ 0

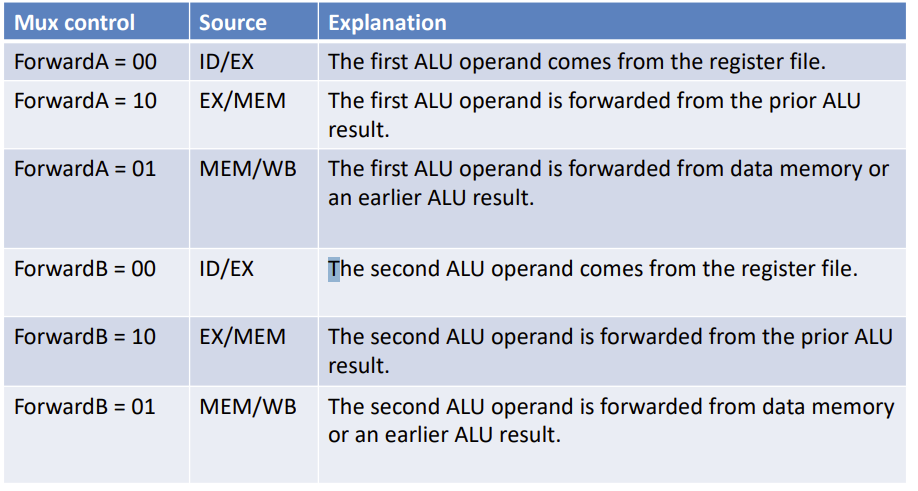

Forwarding Paths

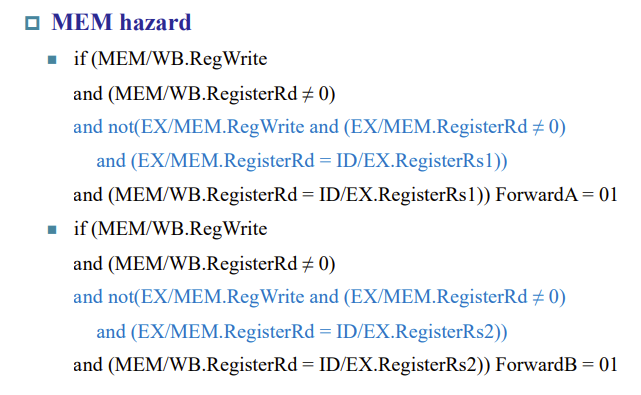

Forwarding Conditions

Double Data Hazard

Consider the sequence

Revised Forwarding Condition

下面这个是描述hazard的语言,要学习,考试会考

不需要死记硬背

你会写黑的就会写蓝的

Datapath with Forwarding

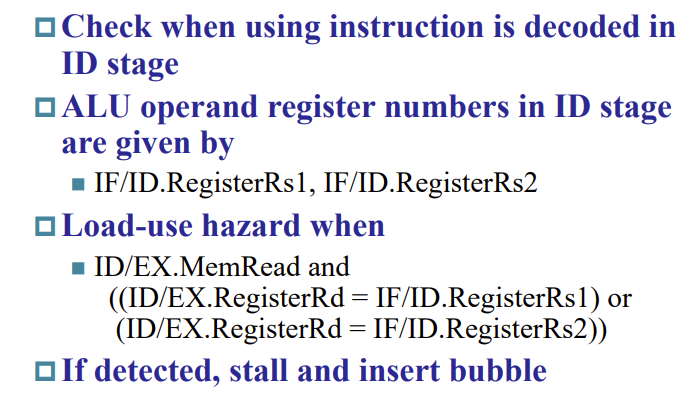

Load-Use Hazard Detection

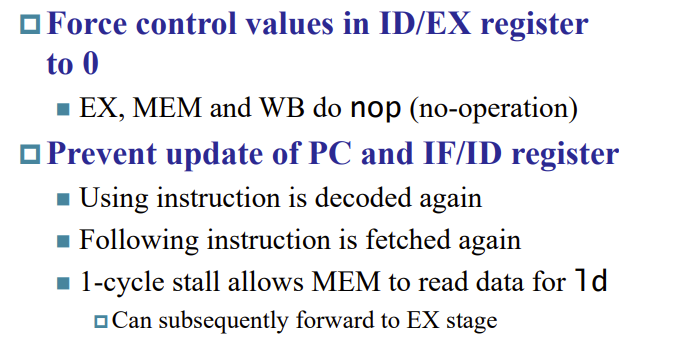

How to Stall the Pipeline

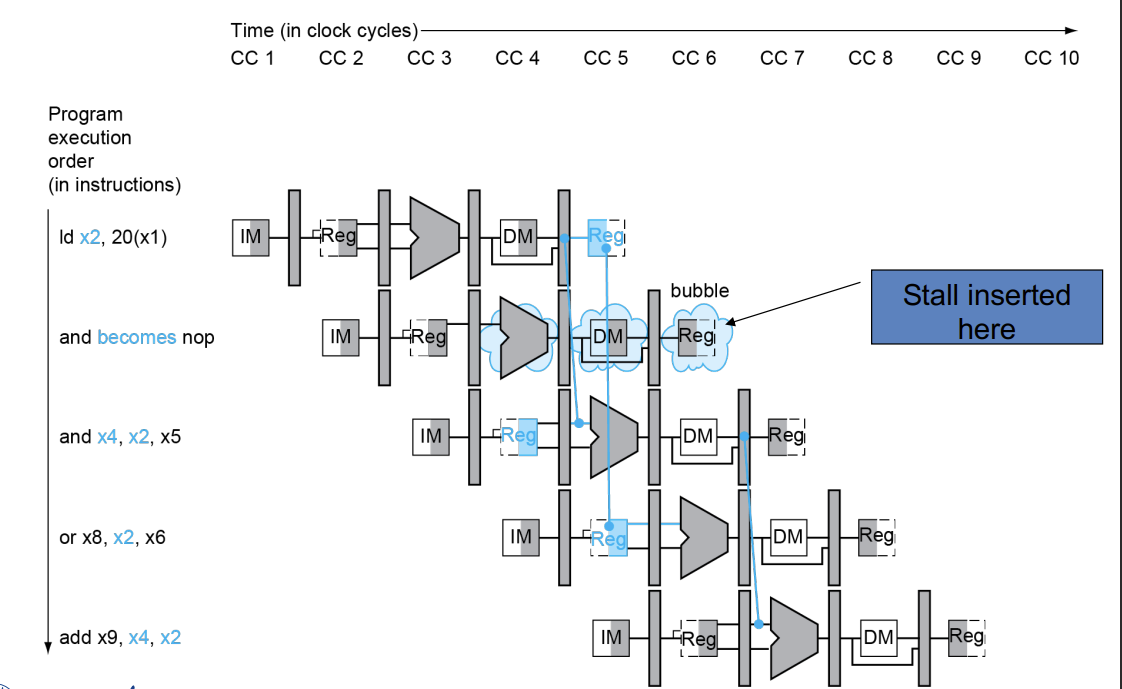

Load-Use Data Hazard

Datapath with Hazard Detection

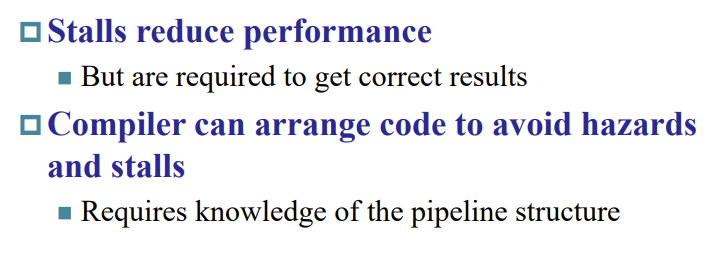

Stalls and Performance

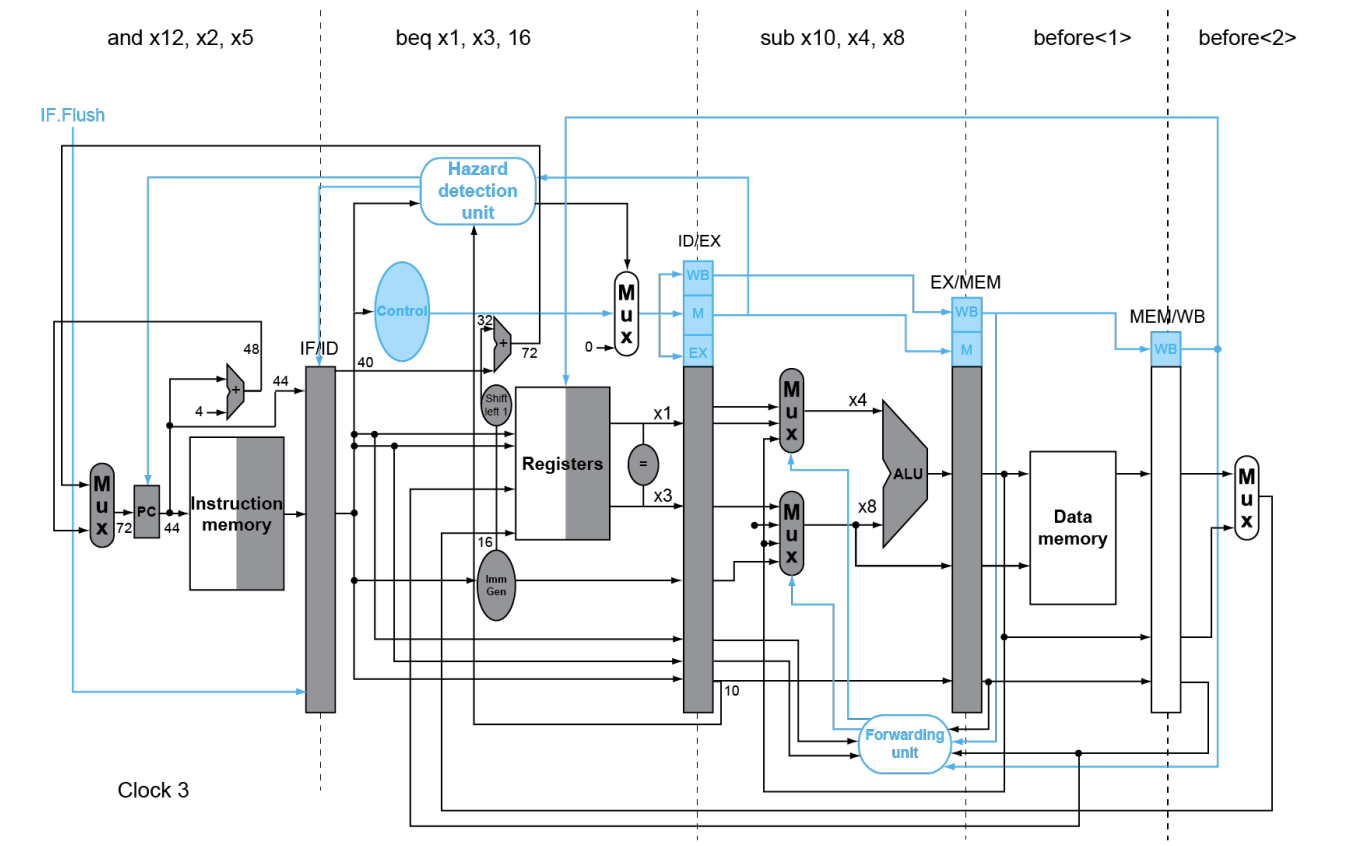

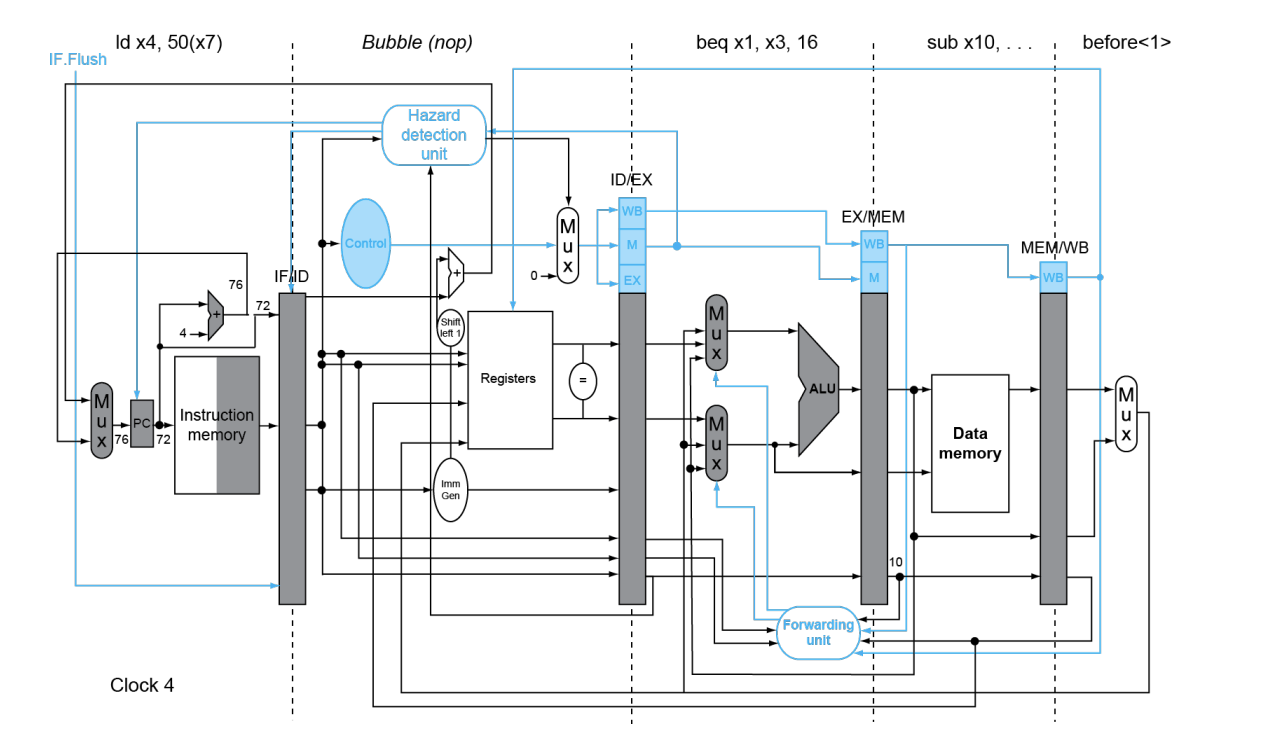

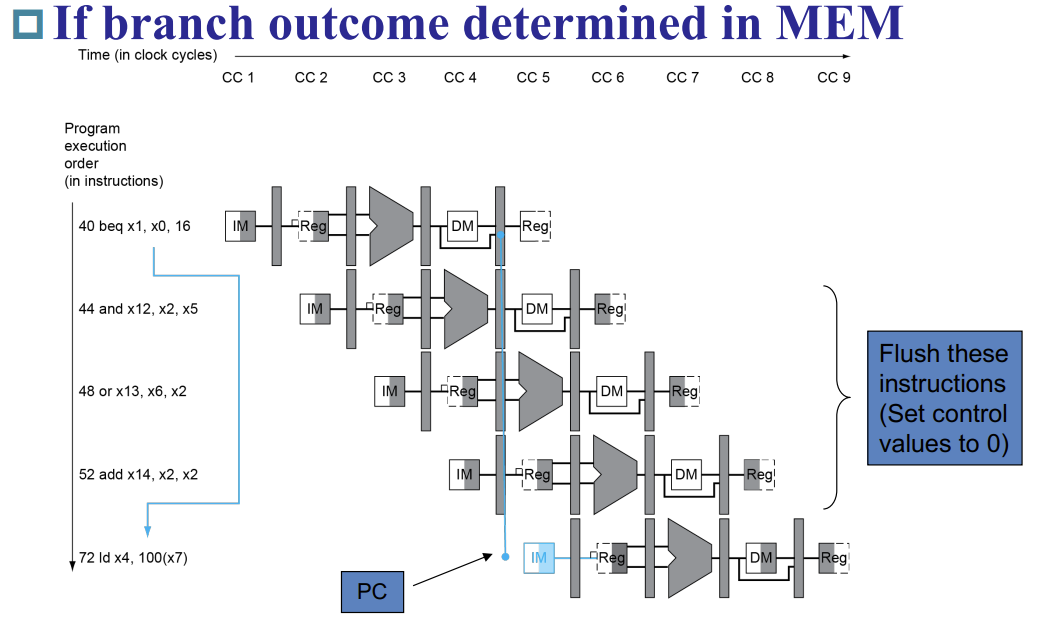

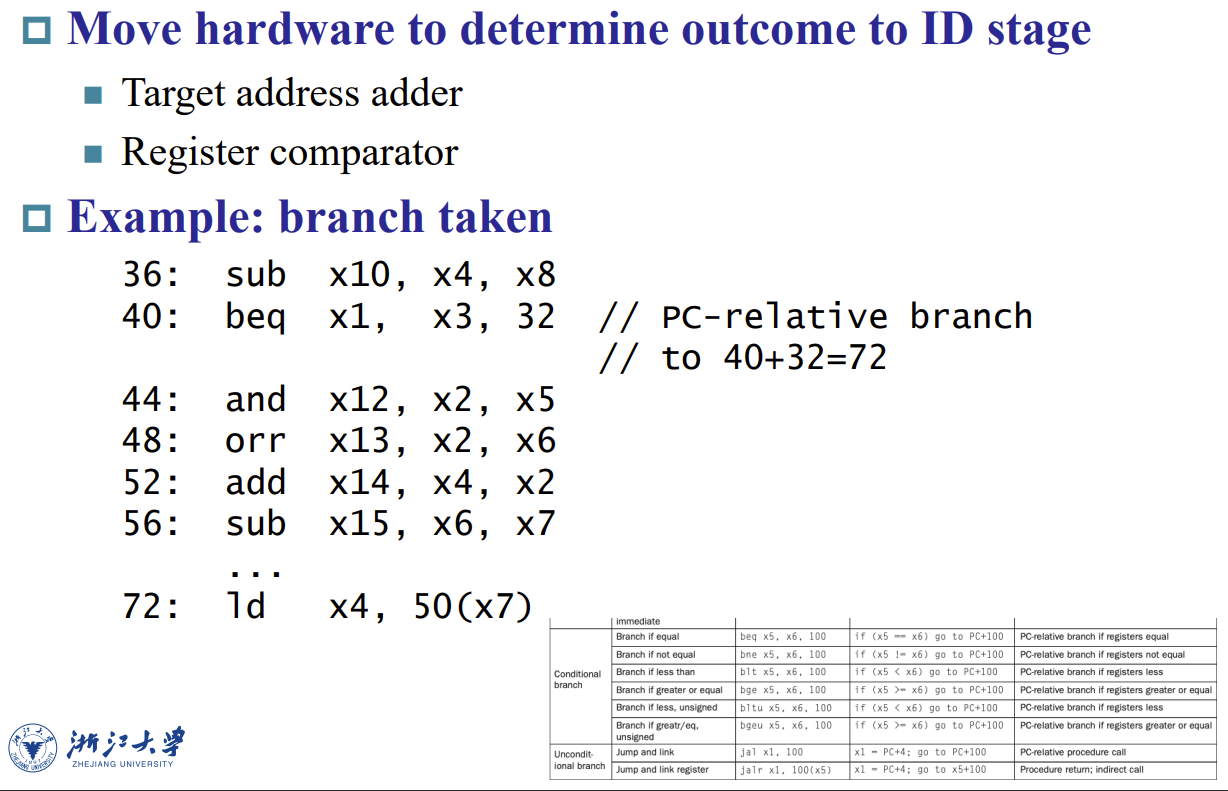

4.8 Branch Hazards

Reducing Branch Delay

Example: Branch Taken

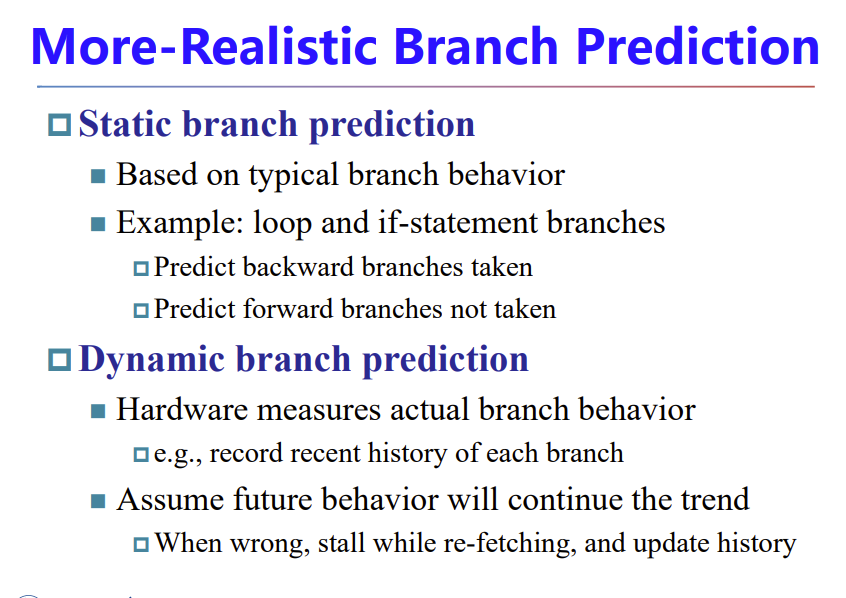

预测

$$