4.1

Chap4 The Processor-Part1

单周期

两个前置步骤

三种指令类型

对于每个指令,先从内存取出(fetch),解码并读取寄存器

再根据指令种类进行具体操作:

- Memory-reference

- Arithmetic-logical

- branches

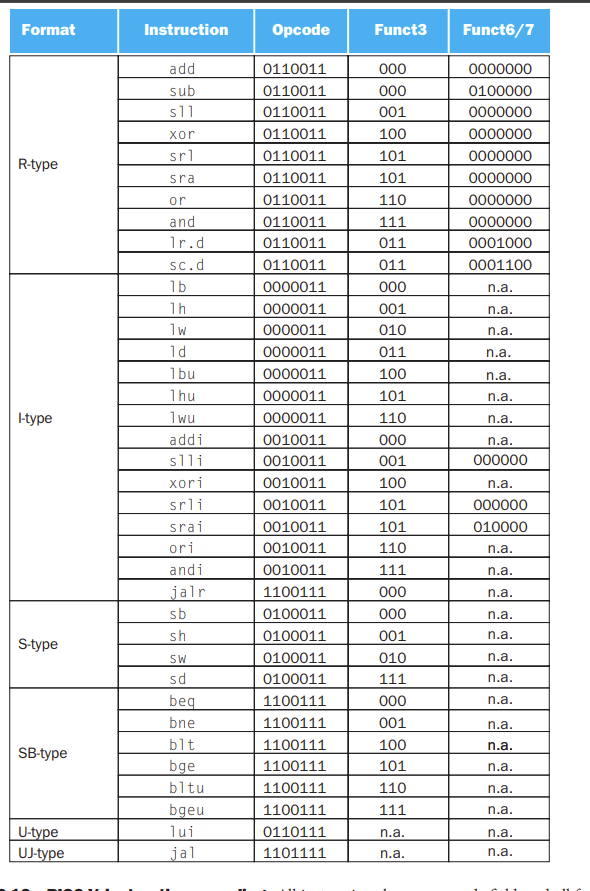

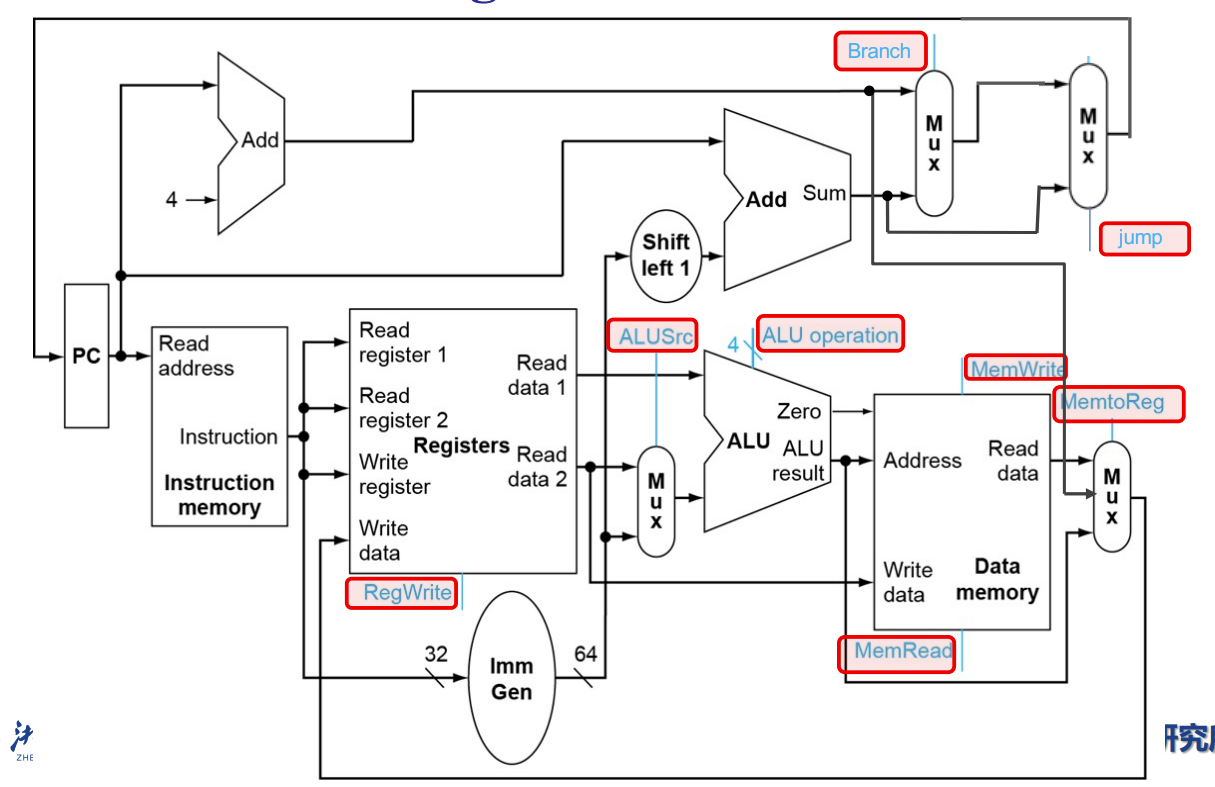

下面是总表

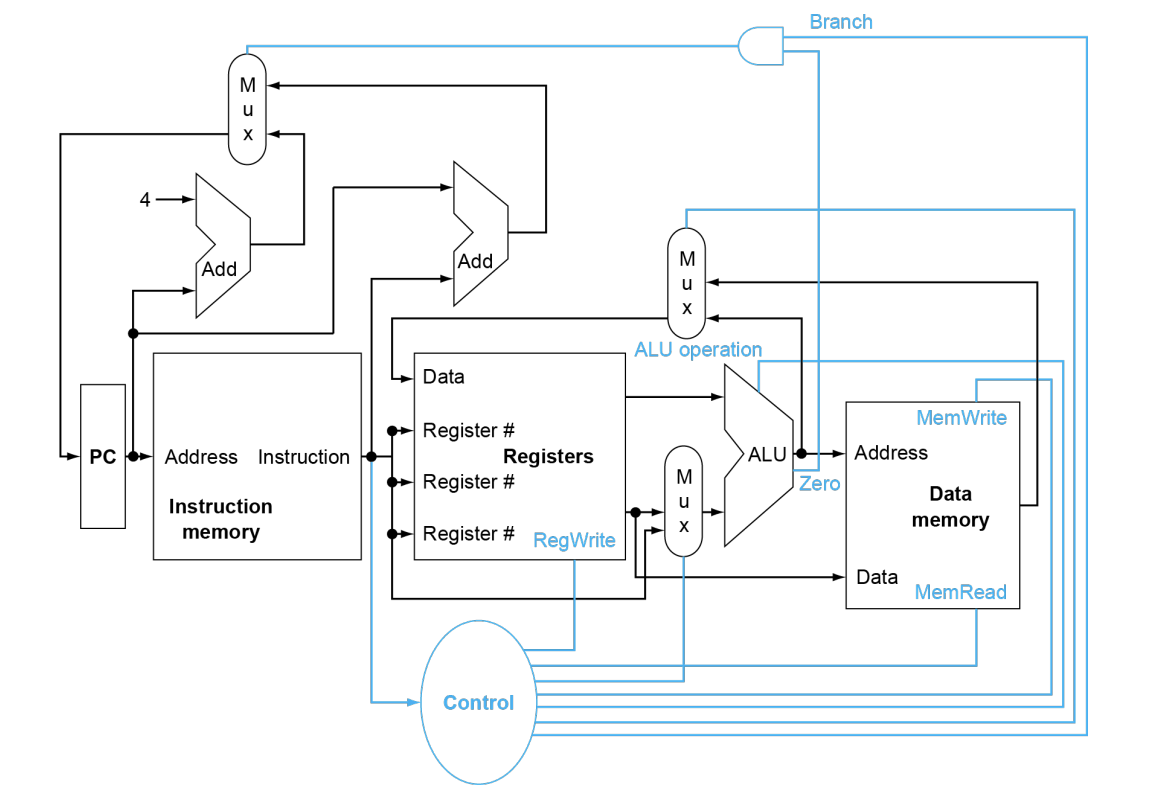

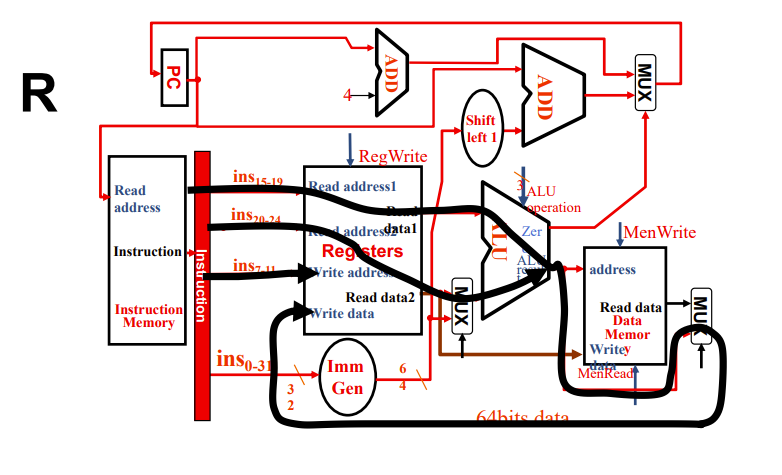

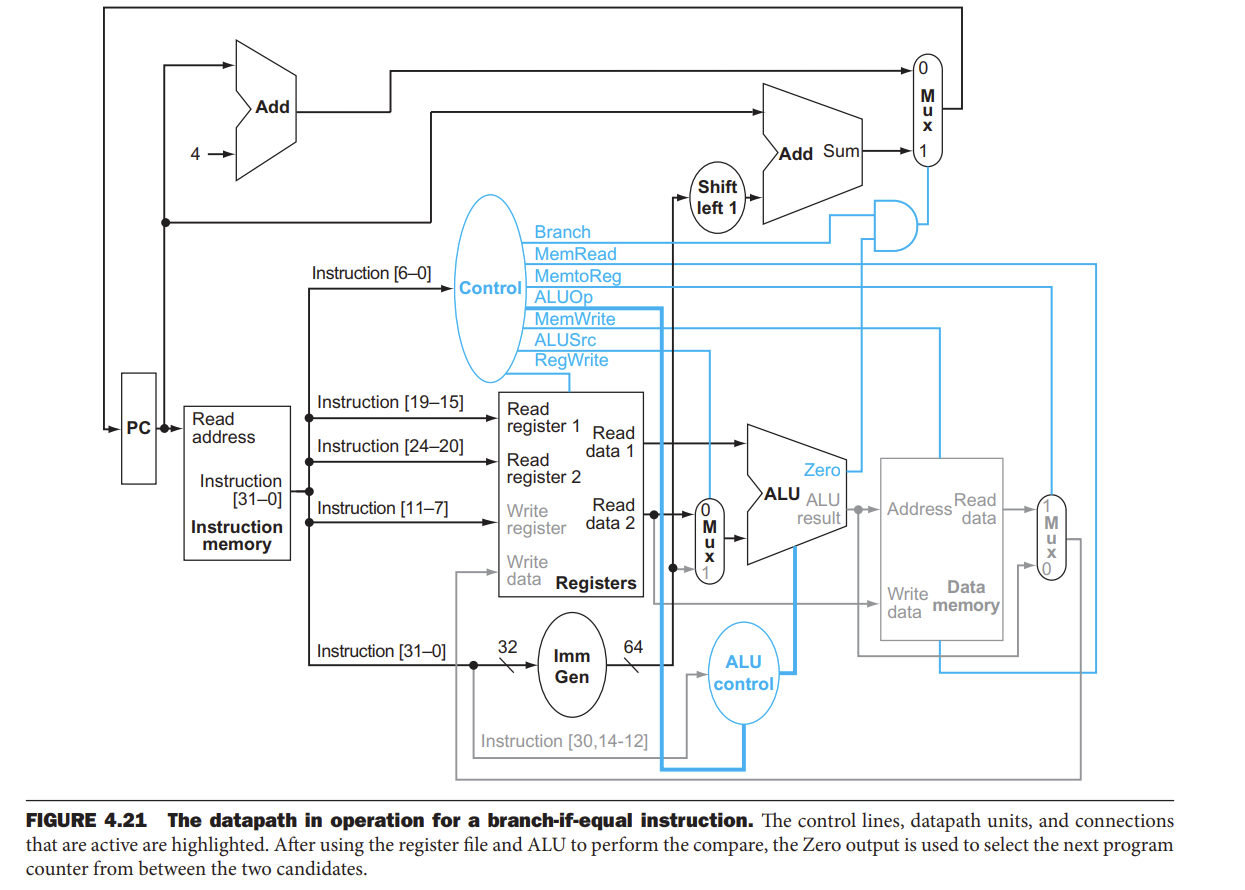

约定,黑的是数据线,蓝的是控制线

注意ALU的zero也是控制信号

图的顶端有个AND,这里的zero表示

beq用ALU判断两个数是否相等的信号(即比较是否相等是用减法实现)有三种情况会将数据写入reg

- ALU计算结果放回reg

- ld指令放回reg

- jalr将返回地址放于reg

不要忘了pc本身是个64bit的reg,放的是指令地址,不是指令

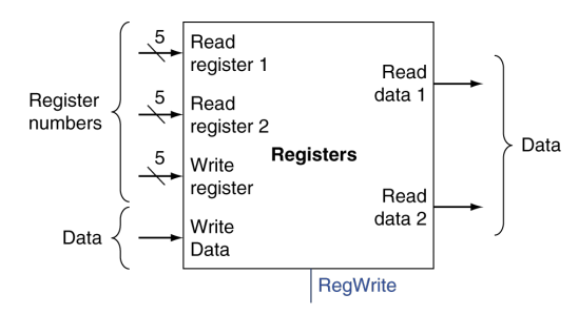

寄存器,x0~x31

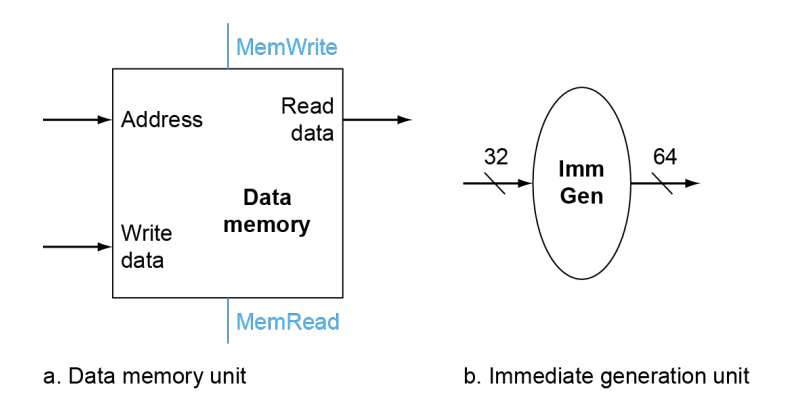

内存与Imm整合模块

注意,内存的地址接口需要提供已经偏移过的地址,所以需要ALU提前将偏移量算进去

Imm整合模块见后文

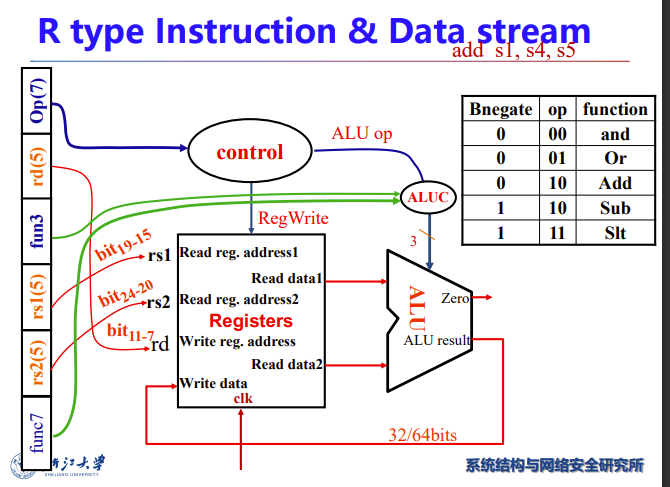

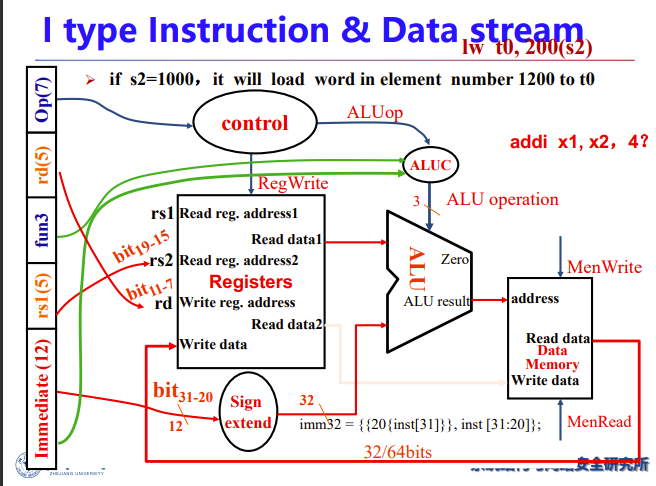

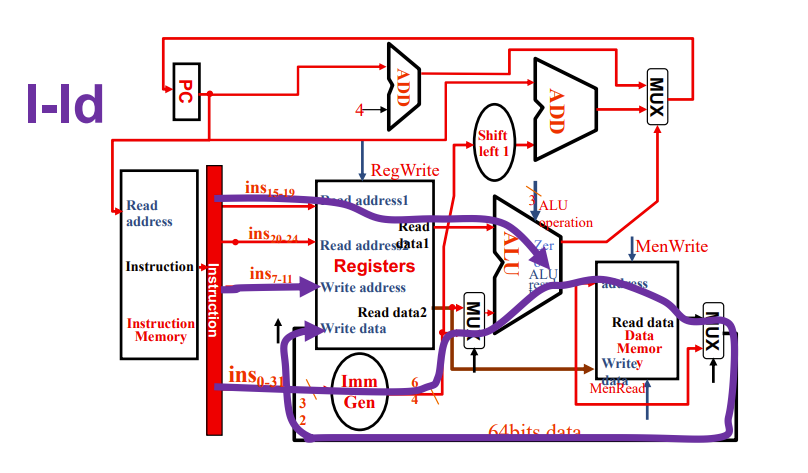

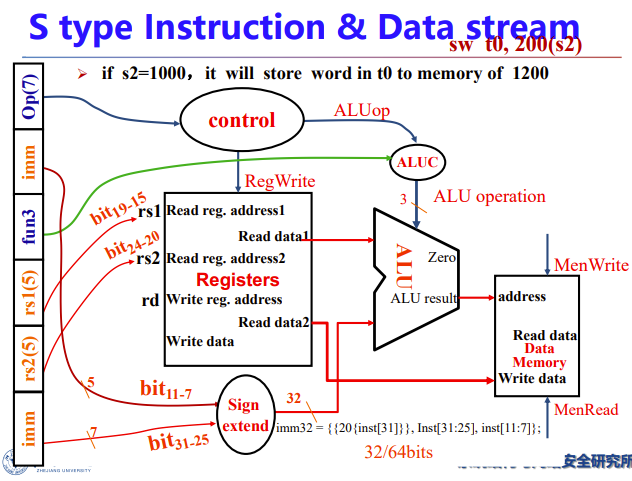

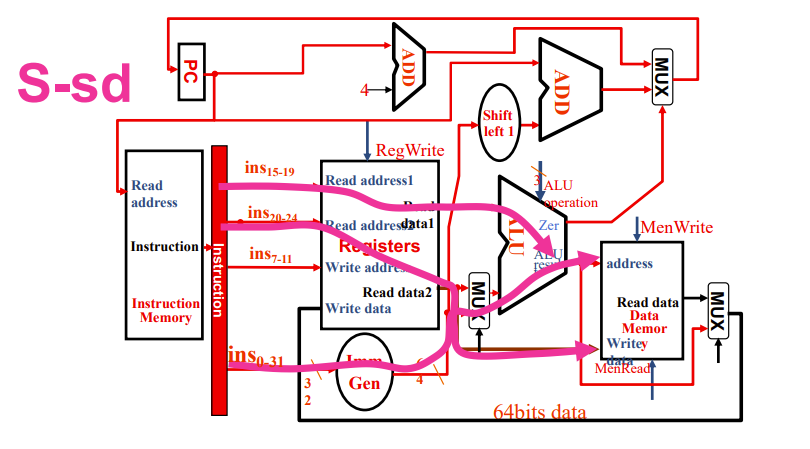

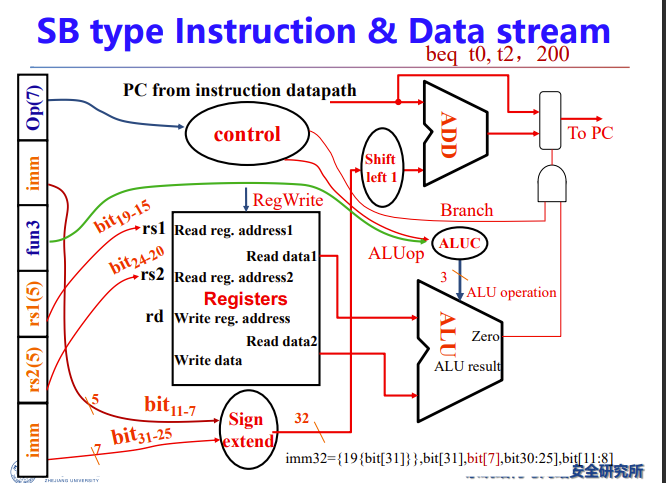

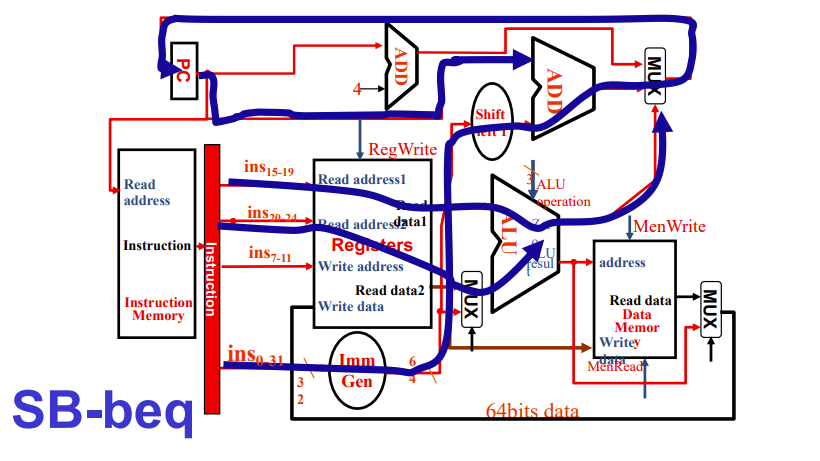

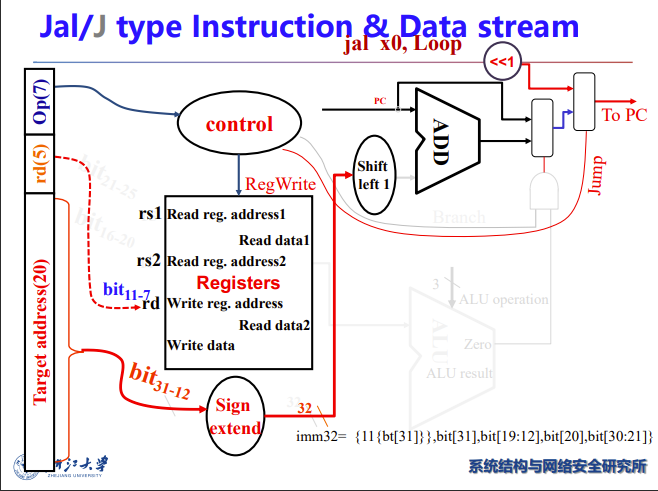

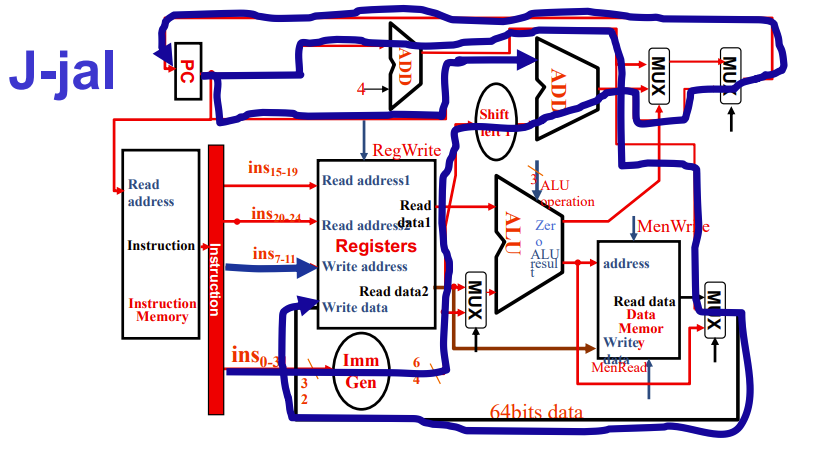

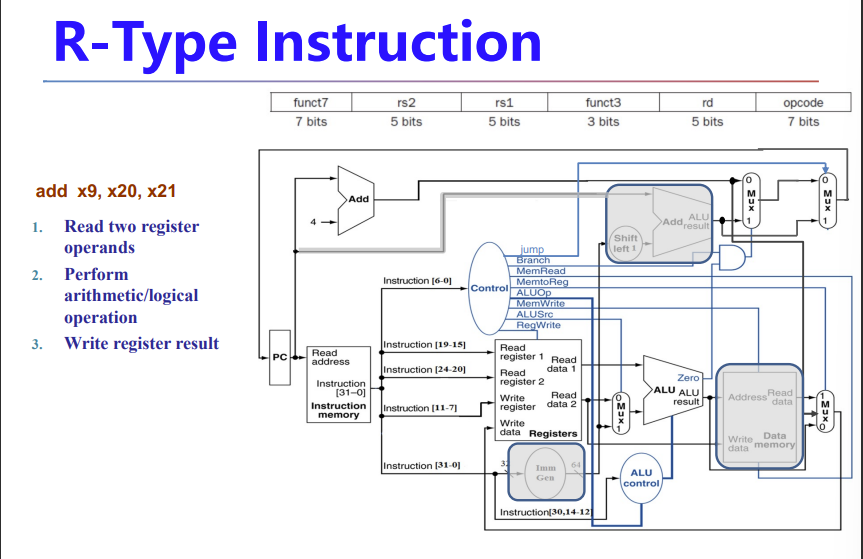

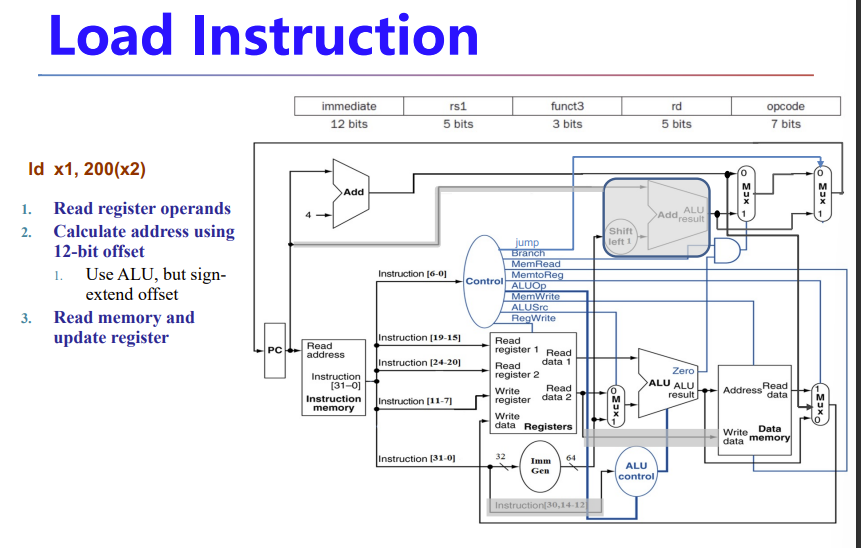

具体各类型指令的链路(注意下面是32位的例子,上面的是64位)

每个指令有两张图,一个表现指令码去向,比较简略;一个指示数据流

红色框是解码部分,解码后将相应的码位输出到对应的地方

右下角的mux有2bit控制信号,图里少了个jump指令返回pc+4的输入

注意上面Sign extend,

imm32={{20{inst[31]}, inst[31:20]}}有符号数拓展

ImmGen用于处理指令里的立即数,比如合并、移位

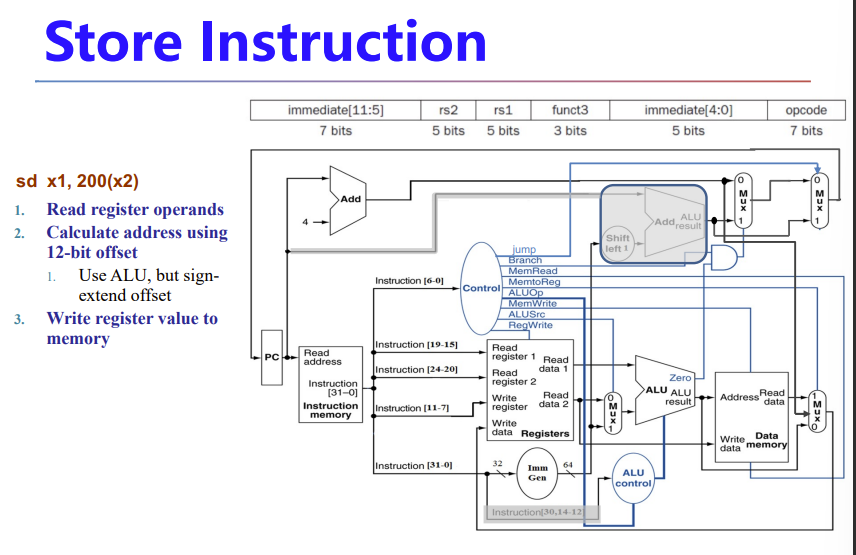

两个mux与R型都不一样了,且需要进入data mem

sd差不多

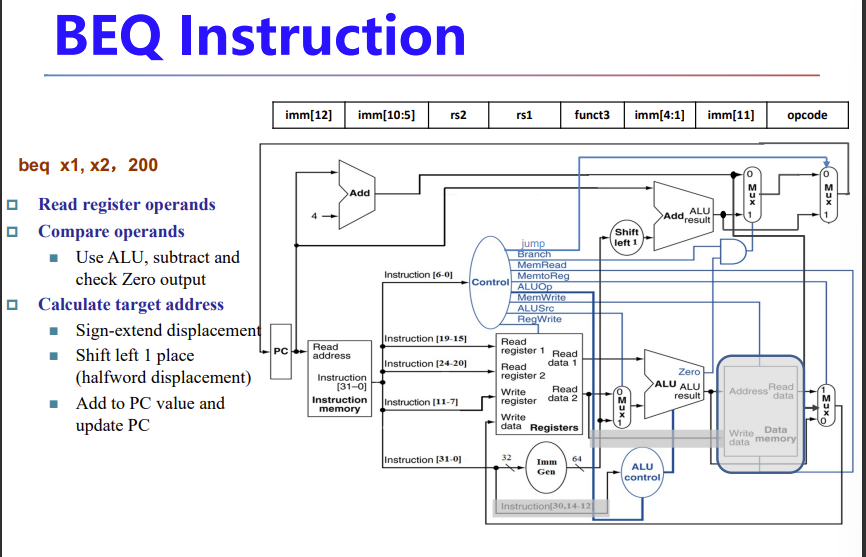

立即数左移了一位,因为,beq指令中的imm是地址偏移量

实际连线时会直接从第二位开始连,不用额外的移位运算,图中只是强调一下

上面有两个add,左边专门pc+4,右边获得偏移后的目标地址

目标地址会直接给pc,结束beq

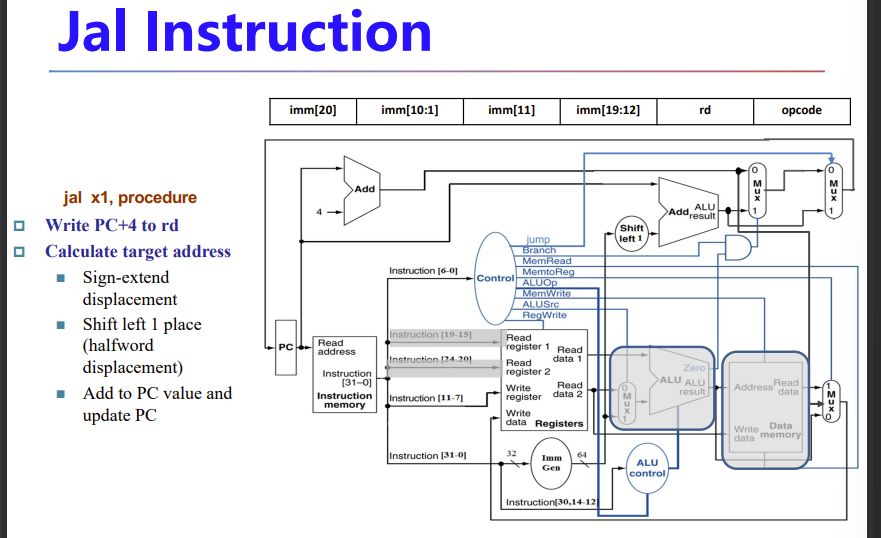

首先是pc+4到MemtoReg到reg,实现

x1=pc+4然后将跳转地址交给pc

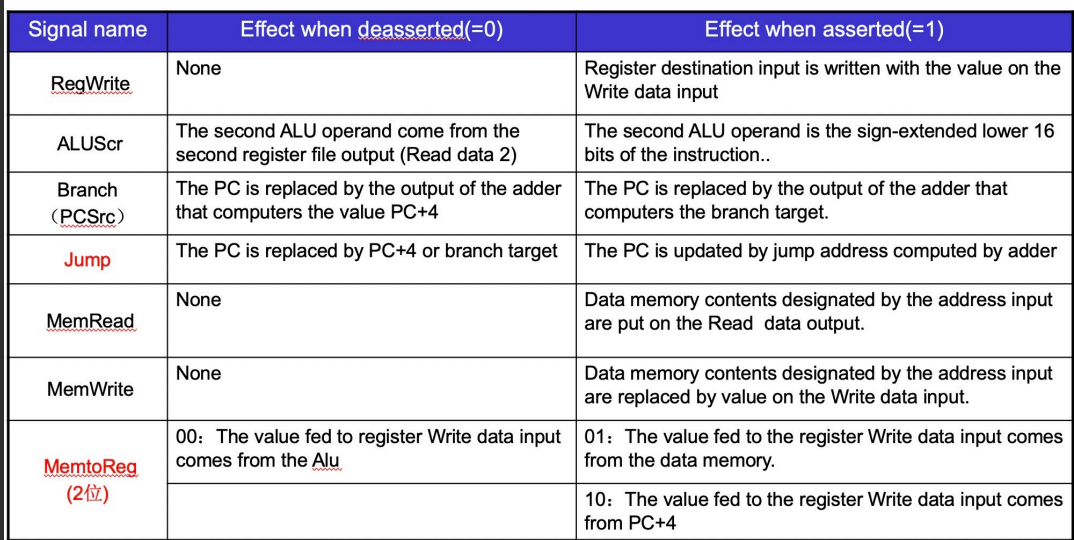

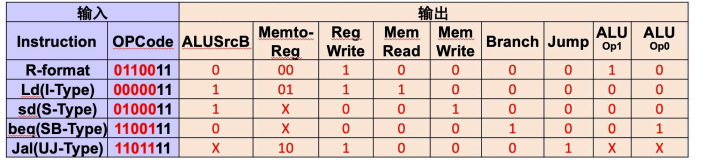

共7+4个信号

controller有7个信号

- RegWrite - Mem

- ALUSrc - Mux

- MemWrite - Mem

- MemRead - Mem

- MemtoReg - Mux

- Branch/PCSrc - Mux

- jump/PCSrc - Mux

ALU operation信号 从controller交给ALU control另外处理4个运算

注意,即便inst没有fuct3和func7,ALU control也能控制ALU。R-type之外的指令ALU都是固定一种运算的。

注意:

- 没用到的mux的信号要写X,表示无关值,不能写0或1,算错

- menWrite和menRead默认情况下都要强制置零

- 前者为了避免误写入(这是不可逆的),后者实际上其实无所谓,但是后面会提到与cache有关

- branch也是强制置零,防止pc被改掉

controller各信号各值的影响:

Scheme of Controller

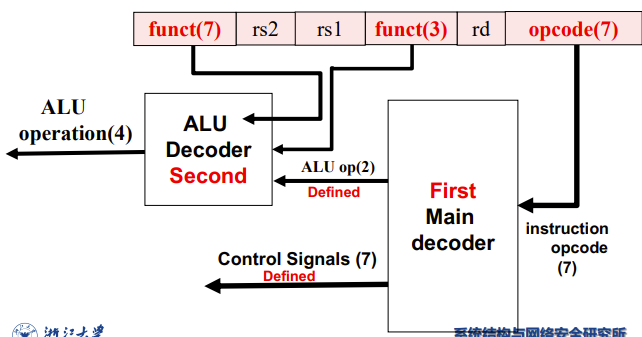

控制信号就是一串二进制数,需要组合电路进行解码

我们分主次两个解码器

- First: Main opcode

- Second: ALU

Controller

这个图要背下来,数据线路和控制线路都怎么连的,有几个bit,哪几个bit

测试会不会,自己画一次

opcode不用记,但是相应的控制信号状态要记

下面是各类指令用到的模块,没用到的府改为灰色

ld是开销最大的指令,所有主要模块都用了