Review 4.2 | The Processor-Diagram

:material-circle-edit-outline: 约 475 个字 :material-clock-time-two-outline: 预计阅读时间 2 分钟

流水线处理器

有空复习一下这个,里面很多例题都没做

指令阶段

一个指令通常被划分为 5 个阶段:

- IF, Inst Fetch,从内存中获取指令

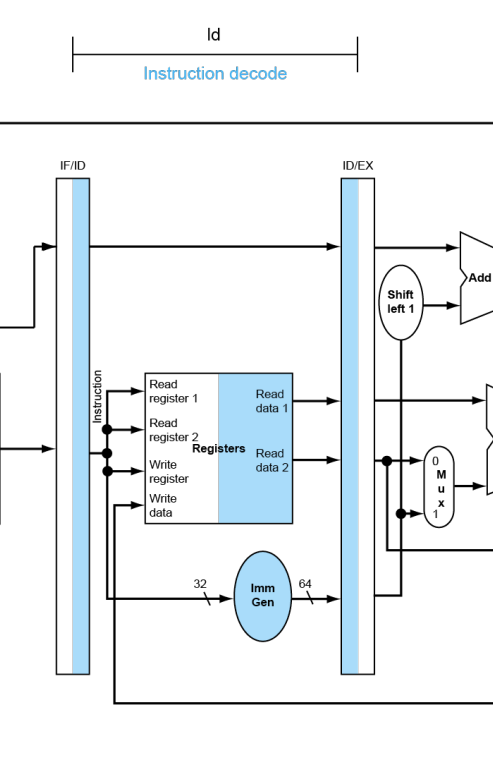

- ID, Inst Decode,读取寄存器、指令译码

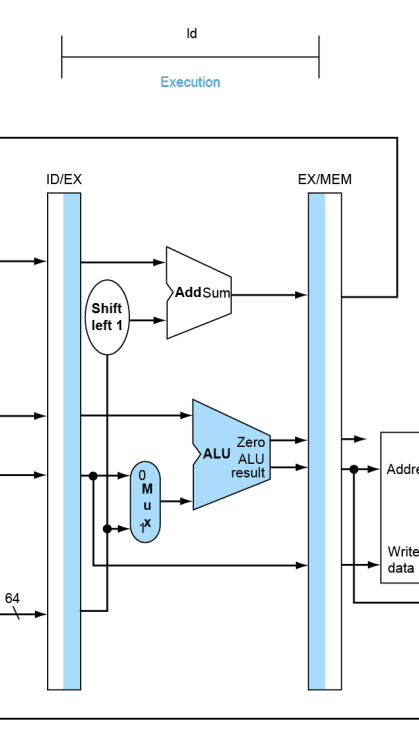

- EX, Execute,计算操作结果和/或地址

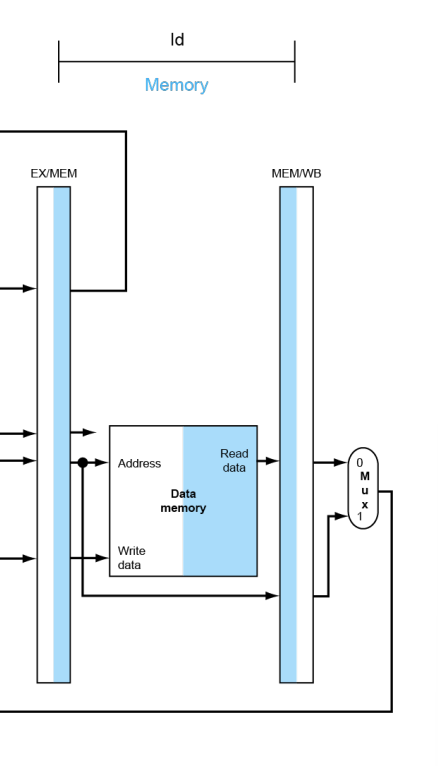

- MEM, Memory,内存存取(如果需要的话)

- WB, Write Back,将结果写回寄存器(如果需要的话)

- CPI is decreased to 1,

- since one instruction will be issued (or finished) each cycle.

- During any cycle, one instruction is present in each stage

任意一个cycle内,都有5个stage同时允许,相当于CPI=1

流水线并没有加速每条指令的响应时间,而是处理器的吞吐量。

处理器的两大评价指标;响应时间,吞吐量(Throughout/)

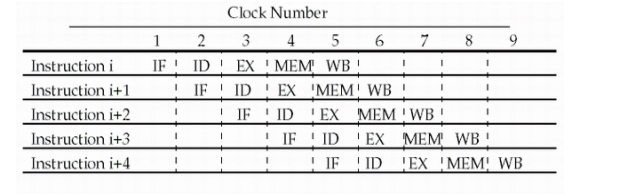

下面是并行的示意图

单周期 CPU 的时钟周期由总耗时最长的指令决定,流水线 CPU 的时钟周期由耗时最长的指令阶段(IF, ID 等)决定。

流水线最大的难点是控制,这也是我们学习的重点

下面我们看看典型的控制会遇到的问题

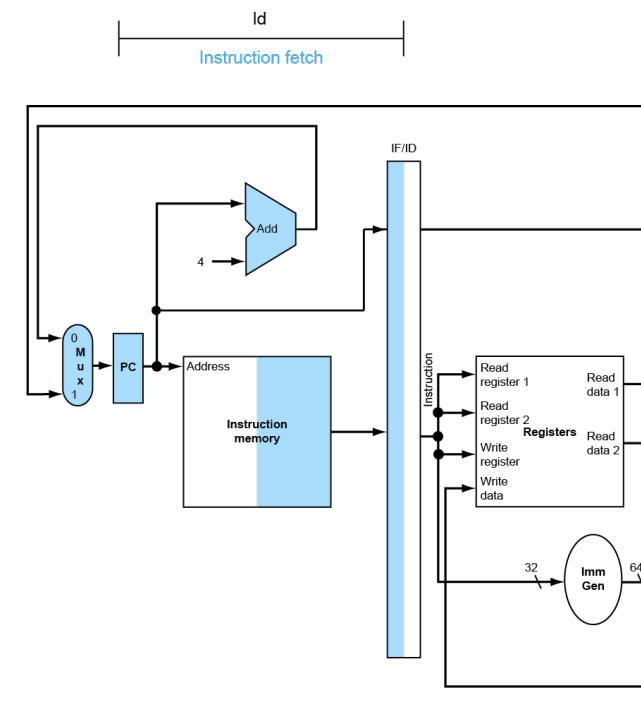

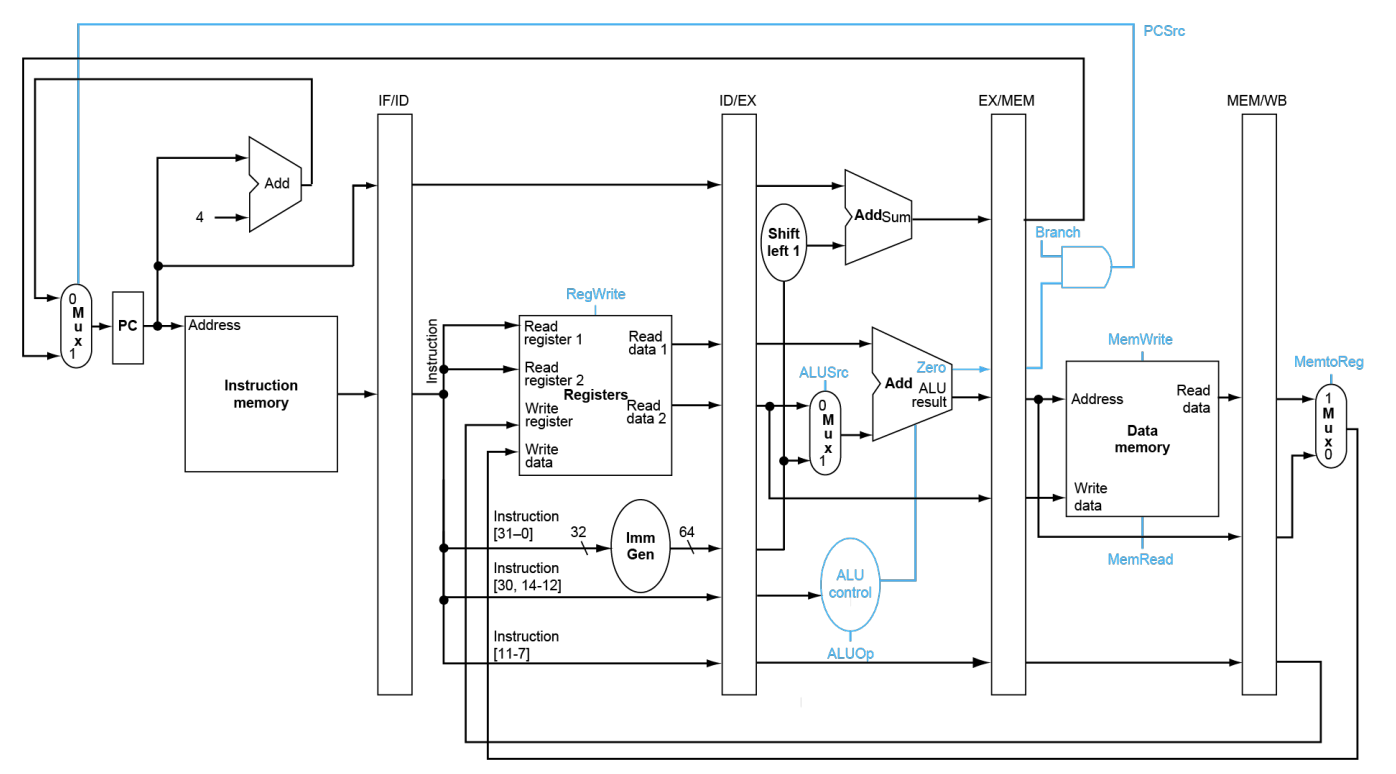

Single-Cycle Pipeline Diagram

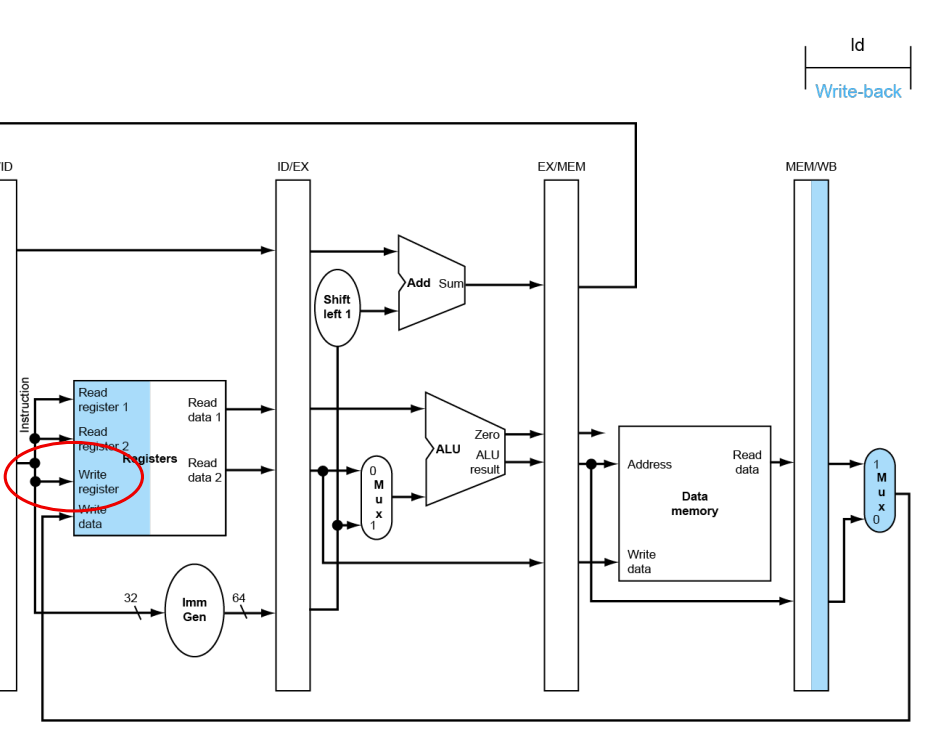

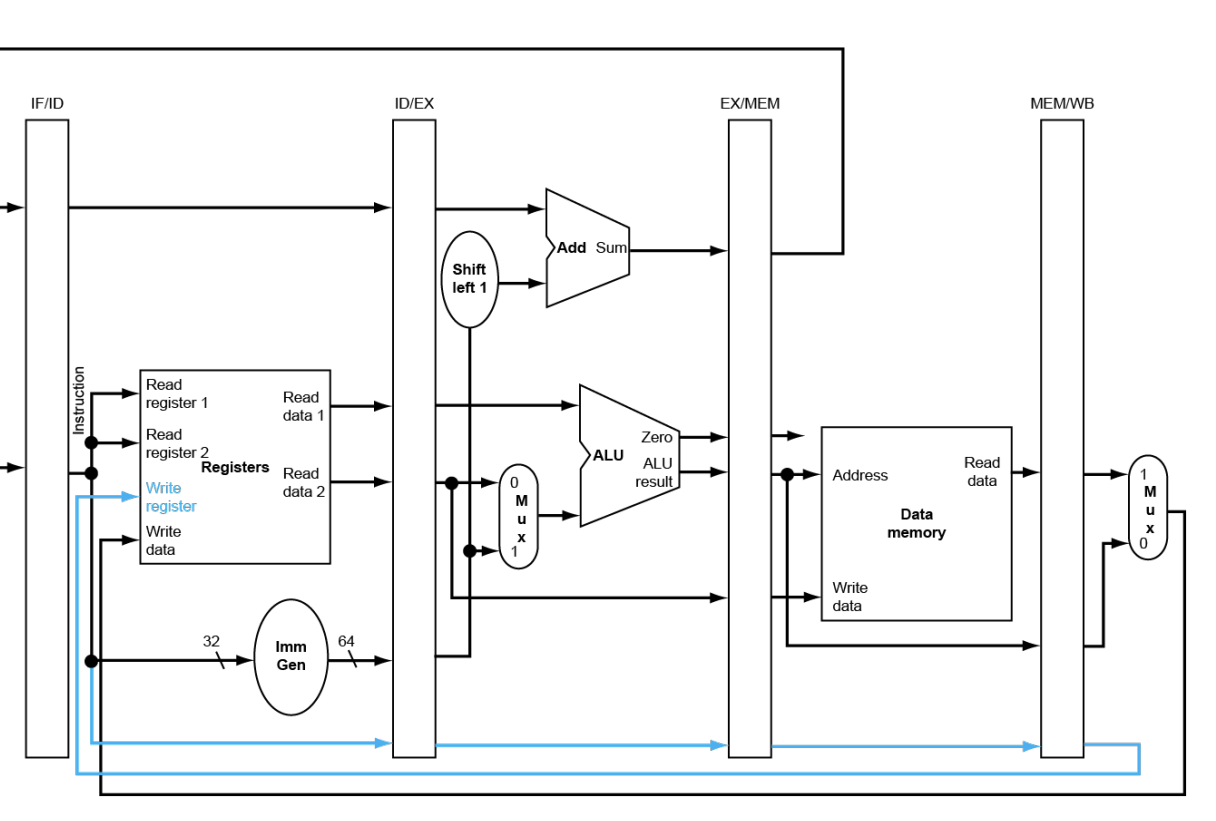

下面这个是错的,这一阶段从regs出来的地址已经不是这个

ld指令的了

下面这张才是正确的,写入的地址是指令里面给的

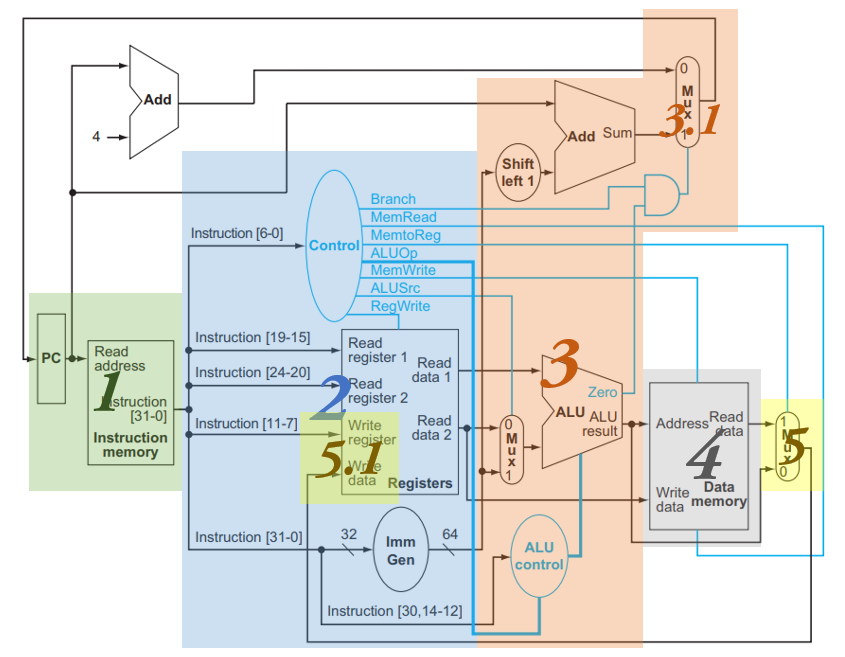

Pipelined Control (Simplified)

下面这图还是之前的单周期信号,但是有个问题,每一阶段都有信号,新的指令读进来会导致信号改变,所以我们需要阶段间用reg储存控制信号

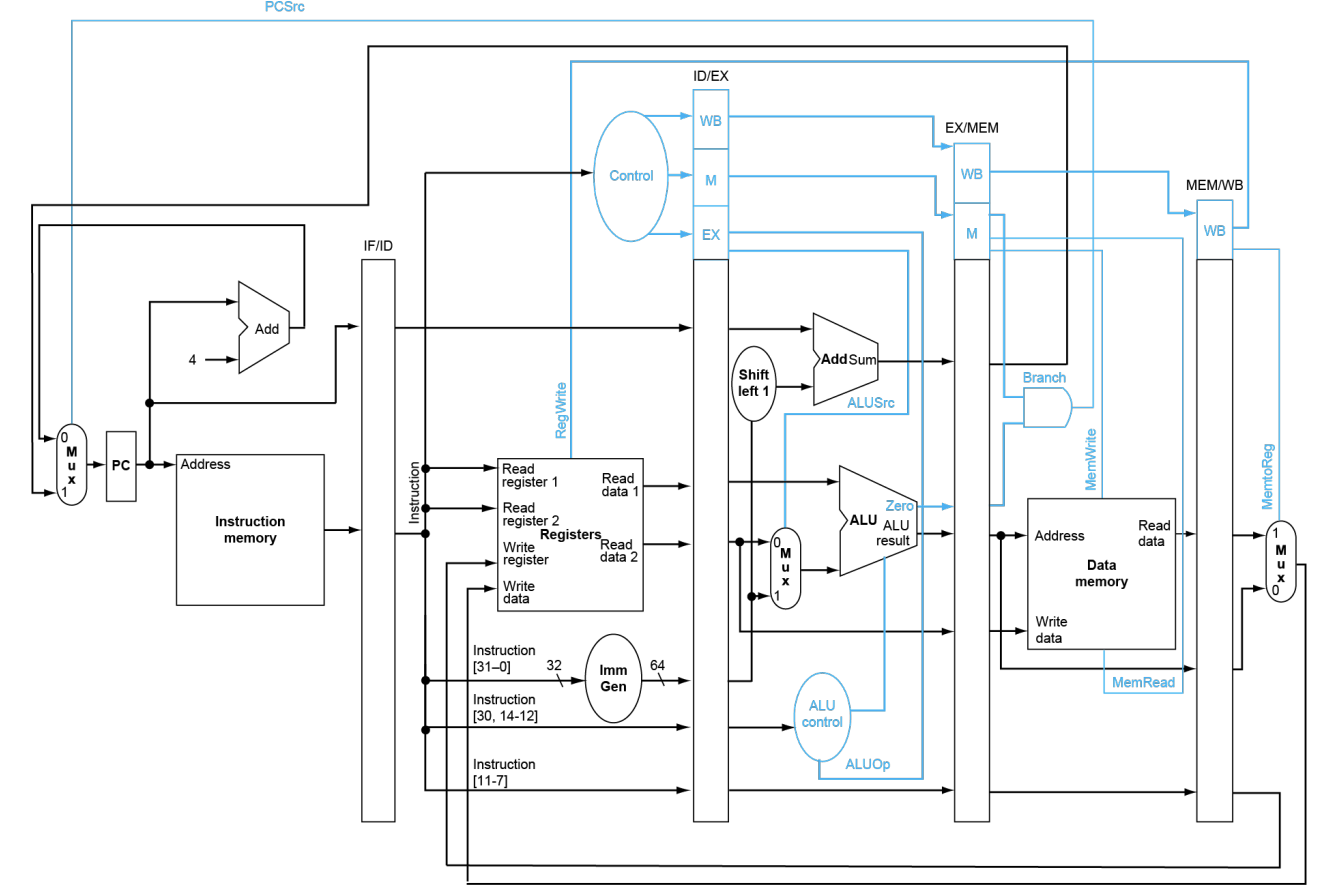

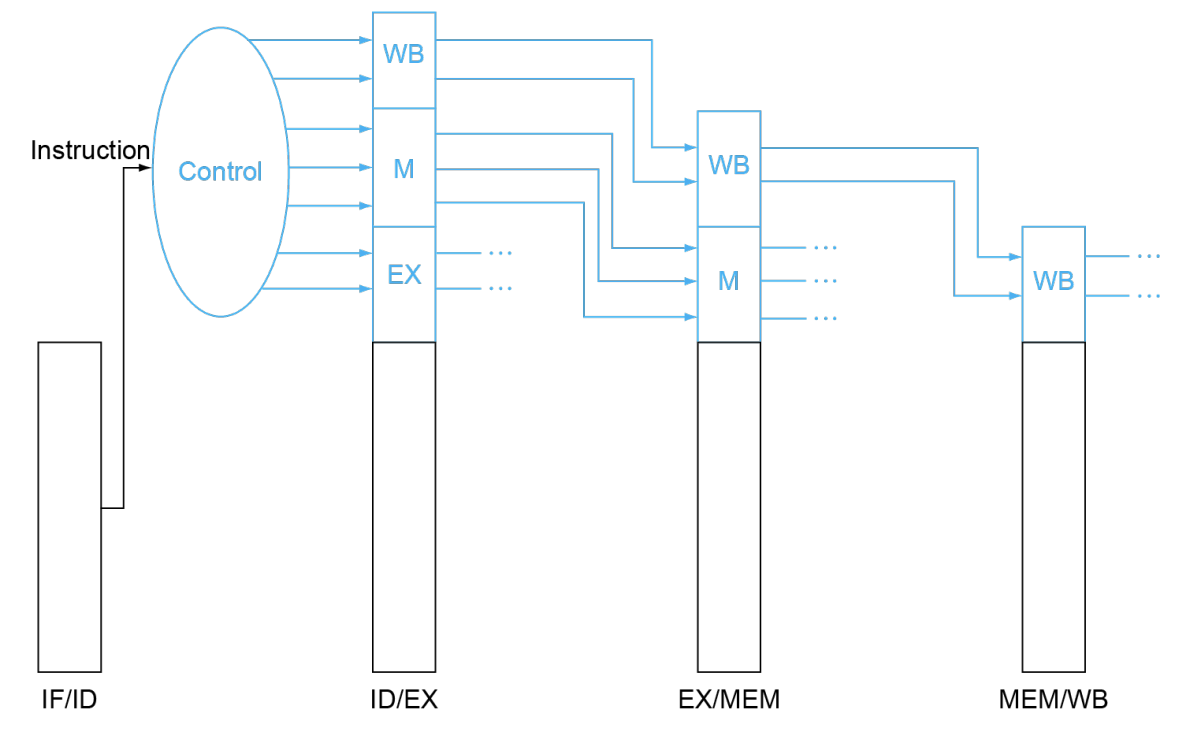

Pipelined Control

下面这个就是将当前指令的各控制信号传递下去,这些蓝色的WB啥的Reg

注意看各个信号是从哪个阶段传过来的

比如ID阶段的RegWrite来自WB阶段