Ch3-- ILP & its exploration

Ch3-0 Extending 5-stage pipeline to support multicycle operations

EX 阶段拓展

我们将尝试缓解结构 hazard

对于一些非 common case,我们目前的五阶段流水线处理器还是有难处的

例如乘法、除法指令,浮点数相关运算等等,其本质要进行几十轮的ALU运算,产生几十个stall

我们希望进行改进,即能支持多周期操作,又不至于打断程序太久

我们可以将 EX 阶段拆分为多个专业的部件 function unit,根据指令类型使用不同部件

我们用两种指标来评价一个流水线里的组件

- latency,function unit time,即指令从输入这个组件到得到结果所经过的cycle

- 还有一个 latency 是指下一条指令等上一条指令多久才能使用 function unit

- 显然其为 function unit time -1 clock cycle

- 我们课上得 latency 特指 function unit time

- 还有一个 latency 是指下一条指令等上一条指令多久才能使用 function unit

- initiation interval,即一个 function unit 面对相同两个操作,一个使用了,另一个隔几个周期才能使用

- 对于完全流水线组件是 1

- 对于非流水线组件是 function unit time

问题

WB写口问题

乱序还可能造成同一个周期内有多个操作到了WB阶段,但EX到WB阶段是只有一条路的,而且如果指令在EX阶段内出现异常,我们还需要只禁止这个指令进入WB阶段,允许其它指令进入

我们借助一个移位寄存器来解决这个问题

Additional Hardware: a shift register+ write conflict logic

对于ID阶段的指令进行检查,如需要进入WB阶段,就在移位寄存器上特定位置置1,这个特定位置是根据从检查到这个指令进入WB经过了几个周期来确定

例如,如果一个指令只在EX指令三个周期就在寄存器第三位 置1,随着寄存器每周期的右移,这个 1会在指令正好离开EX阶段时到达最低位

- 如果对应位置已经置1,就 stall,等一周期再看

最低位会作为 EX/WB 的使能信号,控制通道开关

数据竞争

计组讲的 data hazard 是 RAW,是 true data dependent,只能 stall

WAW 和 WAR 实际上都是命名相关的,就是可以通过换一个寄存器使用来解决的

对 EX 阶段的拓展会造成一个问题,不同操作时长不同,先开始的操作可能比较慢,后来的操作比较快,后来的就先一步进入WB阶段,这就乱序了

RAW

在 ID 阶段检查

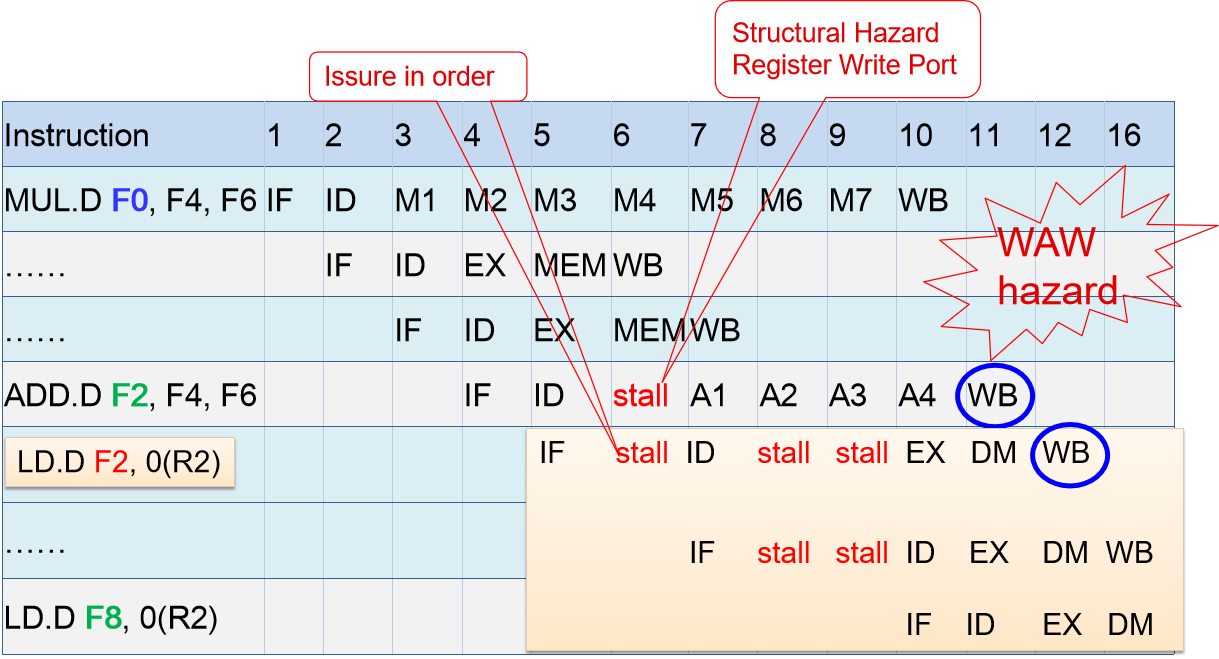

注意一个问题,我们现在的流水线是按序输入,stall 信号是传送到了前面所有阶段的,即 stall 是后面所有指令都 stall,保证指令顺序一致,所以ADD指令IF后有一个stall

WAW

在 ID 阶段检查

WB 阶段的乱序可能会造成的 WAW,就是指相邻的计算操作出现 WB 乱序的情况

原本两个指令A、B先后执行,寄存器上是B覆盖A的结果,但是如果有乱序可能是A覆盖B的结果

解决办法

通过写口寄存器,每条指令置1前检查其后方是否有1,有则 stall,保证 WB 顺序与输入顺序一致

这里 add 的 stall 是写口寄存器没预约上,ld 的 第一个 stall 是为了保持顺序,后面 两个 stall 则也是写口寄存器引起的,通过 stall 强制后一指令的 WB 晚于前一指令,防止错误覆盖

还要注意 stall 时 PC 不动

WAR

原本两个指令A、B先后执行,但乱序之后可能出现B的写先于A的读

逆天,但确实可能发生