Explicit Register Renaming

PPT 计算机体系结构(本)2024-11-04 第 3-5 节

[!ABSTRACT]

tomasulo 算法实现了隐式的 renaming,renaming 是隐含在调度中的

scorebroad 调度算法本身无法实现 renaming,我们需要另外显式地实现

课前小测

Future file

为了实现乱序执行,按序写回,我们就用 future file 先存乱序执行的结果,然后按 issue 的顺序从 future file 写回

如此,我们可以实现按序 issue,乱序 exec,按序 commit

[!OTHER]

还有一个叫 history file 的玩意儿,就是记录所有修改,出问题了可以回退

Explicit Register Renaming

浅谈乱序执行 CPU(一:乱序) - 杰哥的{运维,编程,调板子}小笔记

寄存器重命名的内涵:发生 WAW、WAR hazard 时找一个新的寄存器存放新值

原来的 32 个 reg 是 ISA reg file 的逻辑 reg,是抽象的概念,不是实际存在是,其最终是映射在某个物理 reg 上,在此之前我们都是锁死了这个映射

我们可以额外增加更多的物理 reg 用于 renaming,让逻辑 reg 动态映射到这些物理 reg

记录这个映射关系的表叫 translation table,此外,会有个 FIFO 的 free list 队列链接所有空闲的物理 reg,当 ROB 里的指令 commit 后,其使用的 reg 就会接到 free list 的末尾

IS 阶段会给当前指令要修改的逻辑 reg 从 free list 分配其需要的物理 reg

这项技术可以用于 scorebroad,解决 WAR,WAW

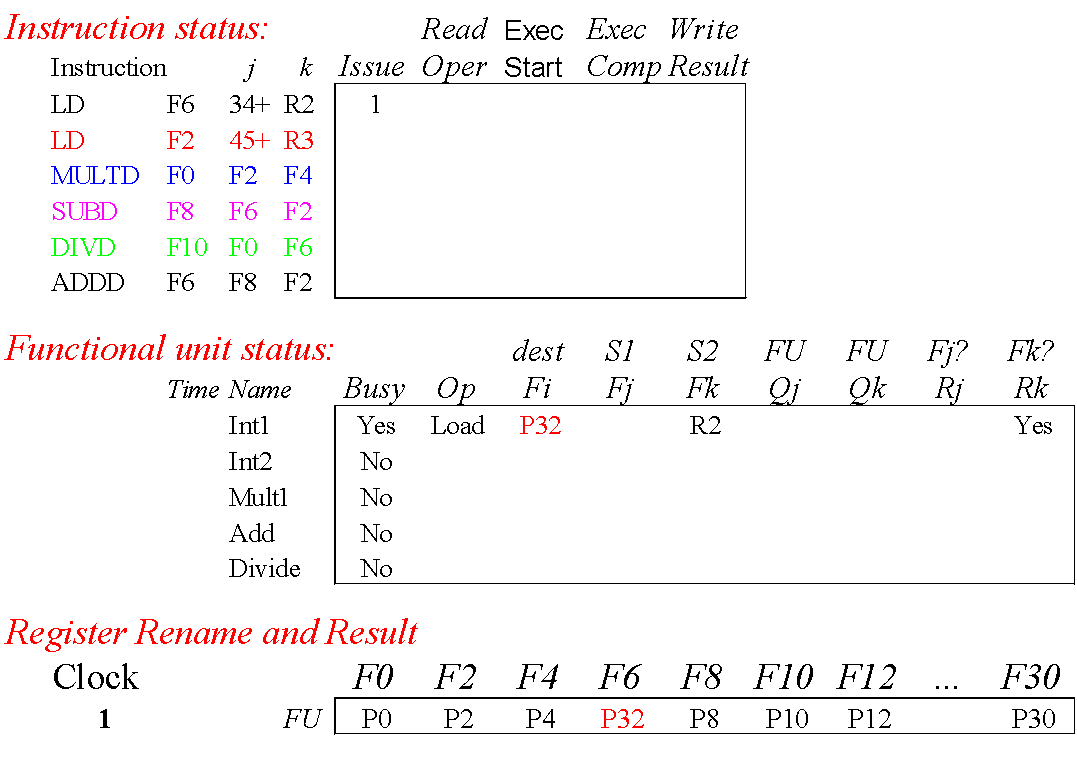

Scoreboard With Explicit Renaming

Four Stages of Scoreboard Control With Explicit Renaming

只有 IS 阶段有变化,其它基本不变

- Issue—decode instructions & check for structural hazards & allocate new physical register for result

- Instructions issued in program order (for hazard checking)

- Don’t issue if no free physical registers

- Don’t issue if structural hazard

- Read operands—wait until no hazards, read operands

- All real dependencies (RAW hazards) resolved in this stage, since we wait for instructions to write back data.

- Execution—operate on operands

- The functional unit begins execution upon receiving operands. When the result is ready, it notifies the scoreboard

- Write result—finish execution

Note: No checks for WAR or WAW hazards!

具体操作

PPT 72 页有例子

第三张表能起到 translation table 的功能

在 IS 阶段,当前指令要修改的逻辑 reg 会被换成新的物理 reg,第三张表更新,读取的就不用改,

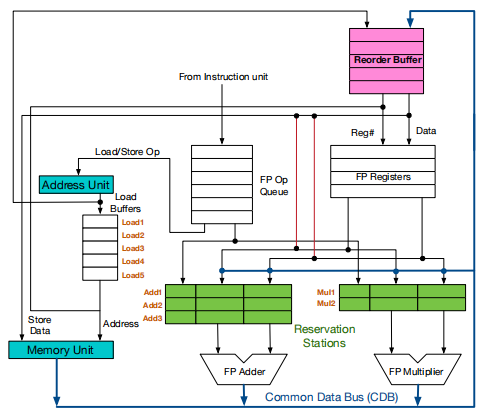

Reorder Buffer(ROB)

这玩意儿我都不知道 jxh 有没有讲,后面上课发现有这玩意儿但没学过就补在这了

其实这玩意儿就是 Future file 的一个具体实现

[!TIP] 为什么我们希望写回的顺序与执行顺序一致

在乱序执行的处理器内核中,处理器会按序发射指令,乱序执行

记分牌算法和 Tomasulo 算法会乱序提交指令,即指令一旦执行完毕且可以写回(记分牌可能因为读后写冲突而不允许写回),那就立刻写回。

乱序提交正是 Tomasulo 最大的缺点,因为冯诺依曼结构向程序员承诺了处理器会按照程序的顺序来执行指令

程序员在调试程序的时候会希望当他在某行代码停下来的时候,代码前面的指令全部执行完,而代码后面的指令一条都没有执行,但是很显然,一个乱序执行、乱序提交的机器是没办法达到程序员的预期的

另外,控制指令、程序异常和外部中断也会截断指令流,所以通过顺序提交指令来实现精确中断(这里的中断是指中断指令流)至关重要

ROB 的目的是让乱序执行的指令被顺序地提交

改进思路

ROB 的核心思想是记录下指令在程序中的顺序

inst 在执行完毕之后不会立马提交(这里的提交指的是修改处理器状态,如修改逻辑寄存器堆),而是先在 Buffer 中等待,等到前面的所有指令都提交完毕,才可以提交结果到逻辑寄存器堆

也就是说,ROB 是一个 FIFO 队列,指令在发射时入队,在提交时出队。

带 ROB 的 Tomasulo

、

、

三点改动:

- 增加了 Reorder Buffer(即 ROB);

- CDB 总线不再直通逻辑寄存器堆,而是直通 ROB;

- inst 需要从 ROB 读取数据。

ROB行为

- For non-Branch instruction

- Update the register with the result

- Remove the instruction from ROB

- When it’s a STORE, update the memory instead of Reg.

- For a mispredicted branch

- ROB is flushed and execution is restarted at the correct successor of the branch

- For a right-predicted branch

- End of branch instruction.