Ch5-2 Cache coherence

掌握监听协议、目录协议,多看例子

计算机体系结构(本)2024-12-09 第 3-4 节 PPT

What is Multiprocessor Cache Coherence?

缓存一致性,即我们希望多个处理器能共享同一个 memory,但处理器实际上是经由各自的 cache 来访问 memory

而且再考虑会直接修改 memory 的 I/O 设备,不一致问题更严重了

单处理器里的 Cache Coherence 问题

在 write back cache 下,cache 和 memory 的数据会不一致,而 I/O 设备是直接访问 memory 的,导致 I/O 访问的数据可能过时的

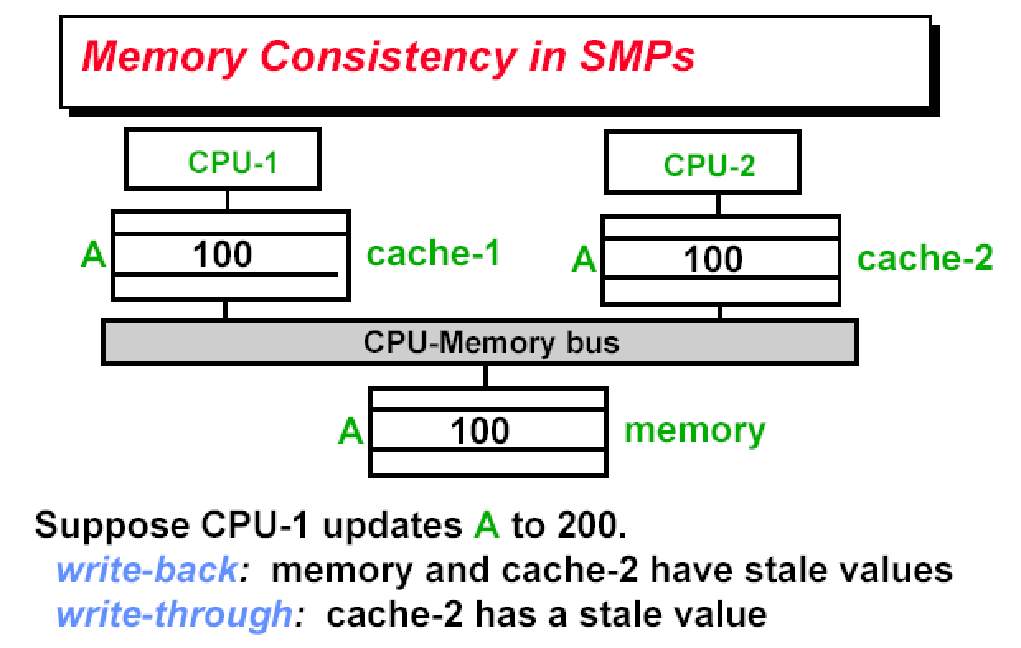

多处理器里的 Cache Coherence 问题

Cache incoherence due to write

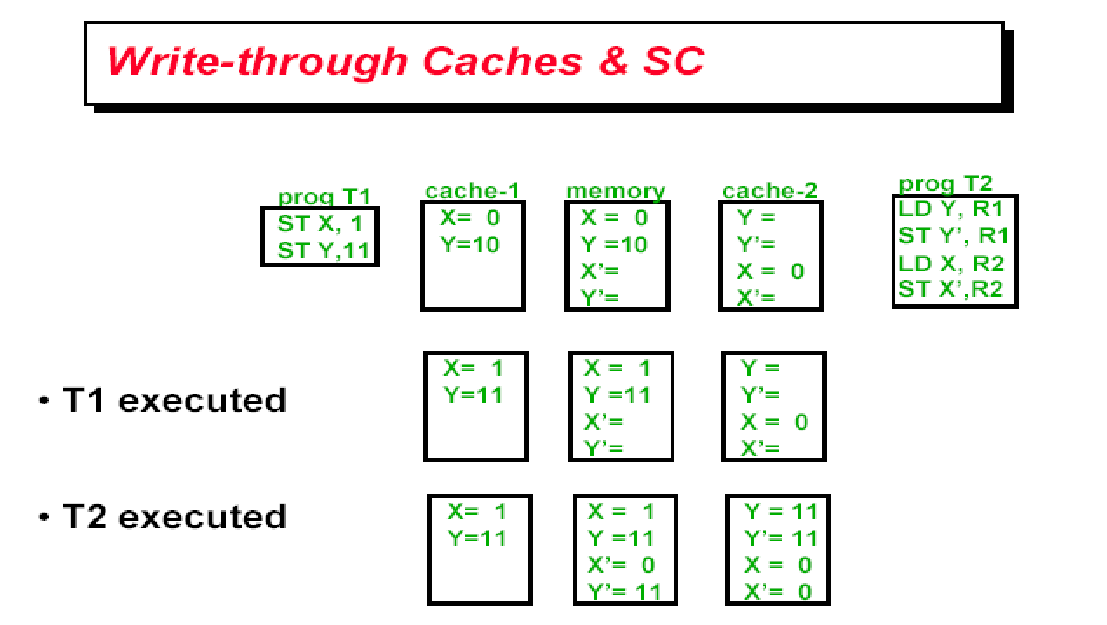

write through 也会有不一致问题

What Does Coherency Mean?

Informally: Any read must return the most recent write(很难)

Better:

- Any write must eventually be seen by a read

- All writes are seen in proper order (“serialization”)

Two rules to ensure this:

- If P writes x and P1 reads it, P’s write will be seen by P1 if the read and write are sufficiently far apart

- Writes to a single location are serialized: seen in one order

Definition of Cache coherence

- P1 Read [X] => P1 Write [X] => P1 Read [X] will return X

- P2 Read [X] => P1 Write [X] => will return value written by P1

- P1 Write [X] => P2 Write [X] => Serialized (all processor see the writes in the same order)

Snooping solution(Snoopy Bus 监听总线)

加一条总线,各处理器写了值,就进行广播,其它处理器的 cache 保持监听,以此更新自己相应的数据

Snoopy Bus 强制一次只能有一个广播,因此实现了 Write serialization

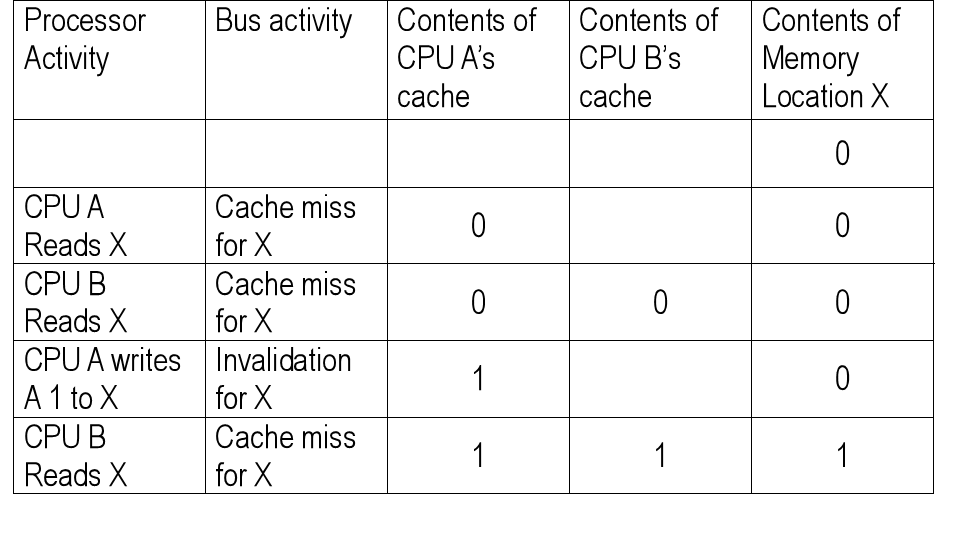

Write Invalidate Protocol

Multiple readers, single writer

一个处理器写了一个值,就广播告诉其它处理器的 cache 你们的这个数据副本是无效的

[!QUOTE]

Write to shared data, then an invalidate is sent to all caches which snoop and invalidate any copies

其它处理器要读这个数据时就 Read Miss:

- Write-through: memory is always up-to-date

- Write-back: snoop in caches to find most recent copy

read miss 的信息会广播,修改数据的那个处理器会将数据写回 memory,再让 read miss 的处理器去读取

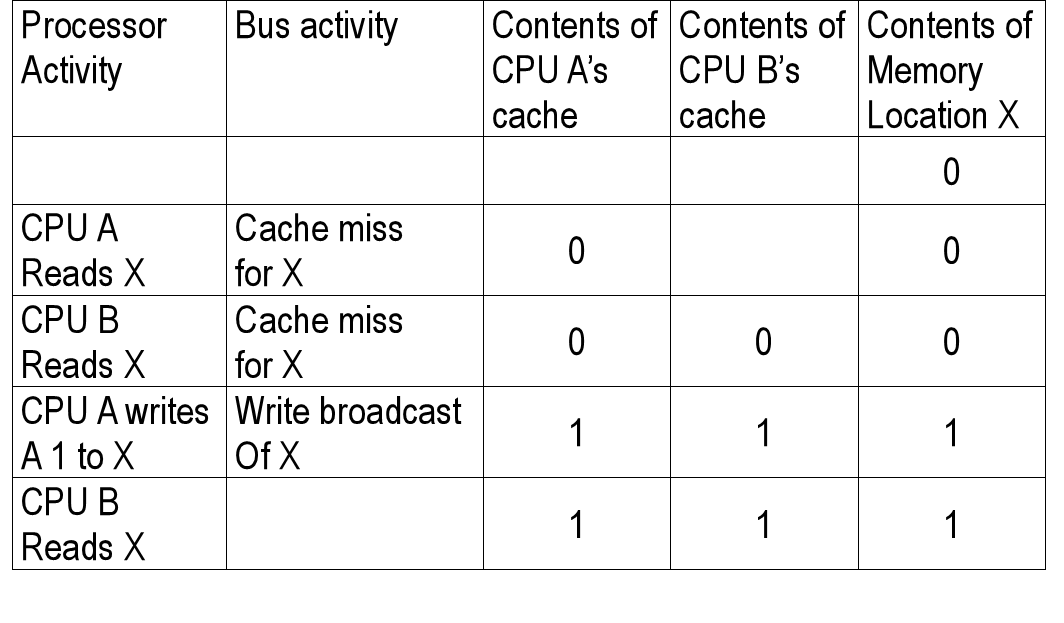

Write Broadcast Protocol

typically in write through

就是把写的数据进行广播,其它处理器进行更新

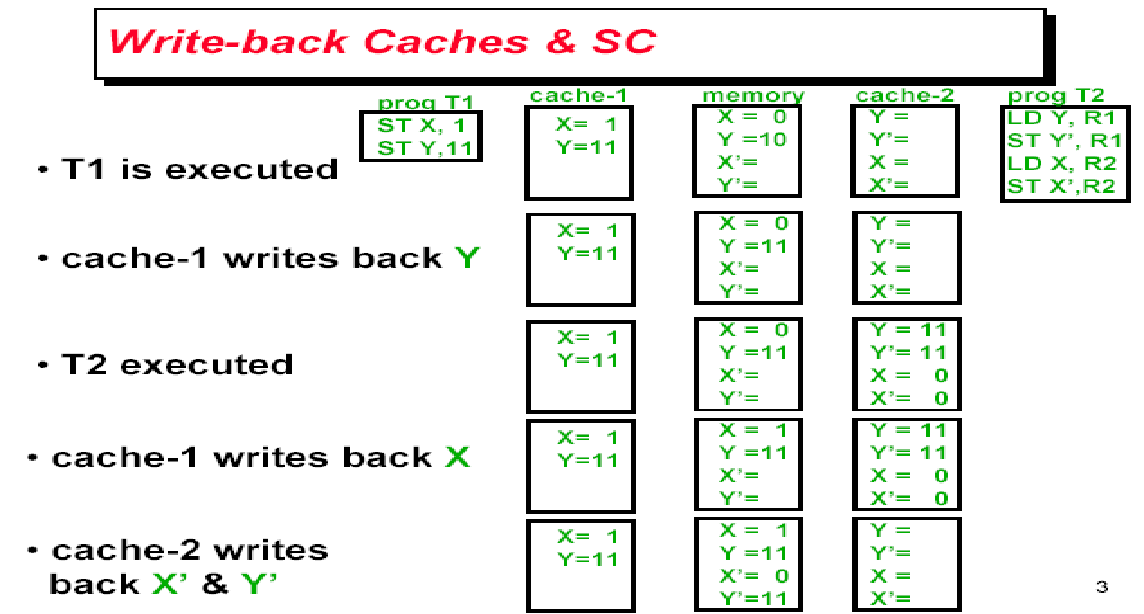

[!EXAMPLE] write back Cache, write invalidate

Broadcast address of cache line to invalidate

All processor snoop, then invalidate if in local cache

[!EXAMPLE] Write back Cache, update

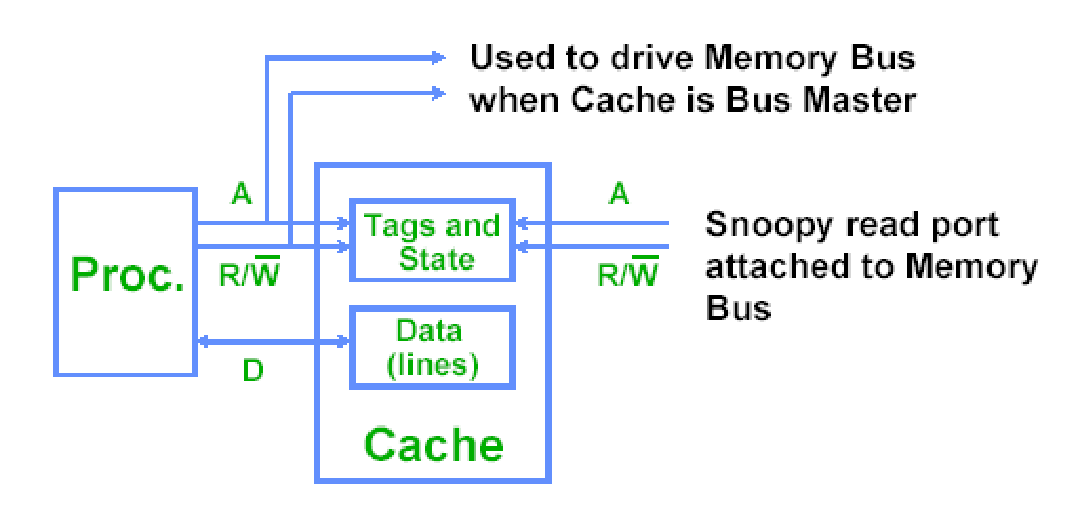

Bus-based protocols (Snooping)

bus 接收的、进行广播的事件分两类:

- Processor

- events from own processor

- Read (R), Write (W), Writeback (WB)

- Bus Events

- events from other processors

- Bus Read (BR), Bus Write (BW)

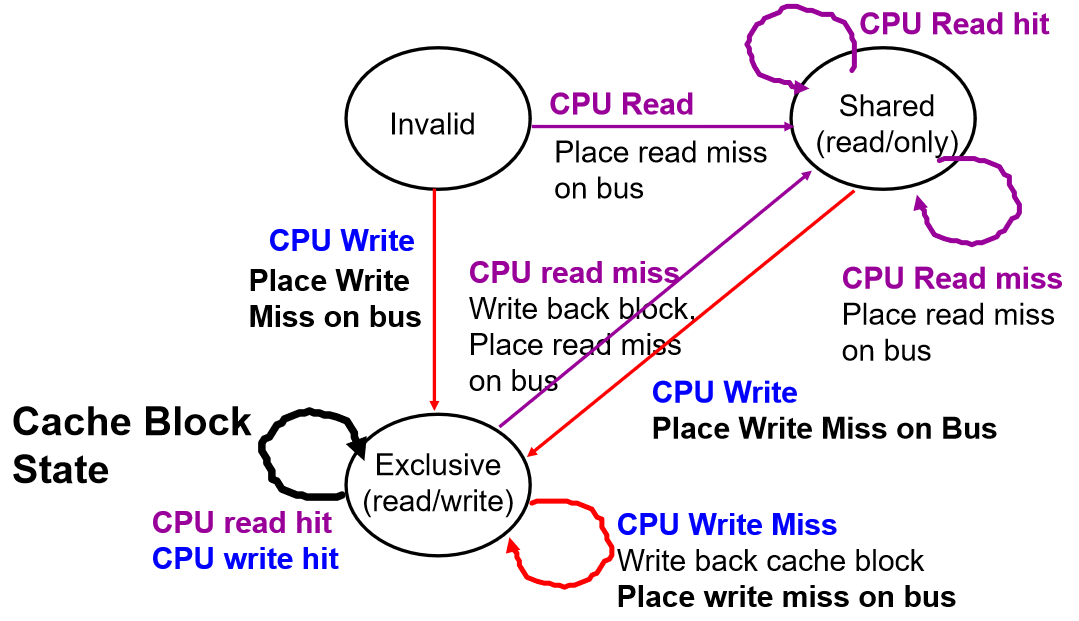

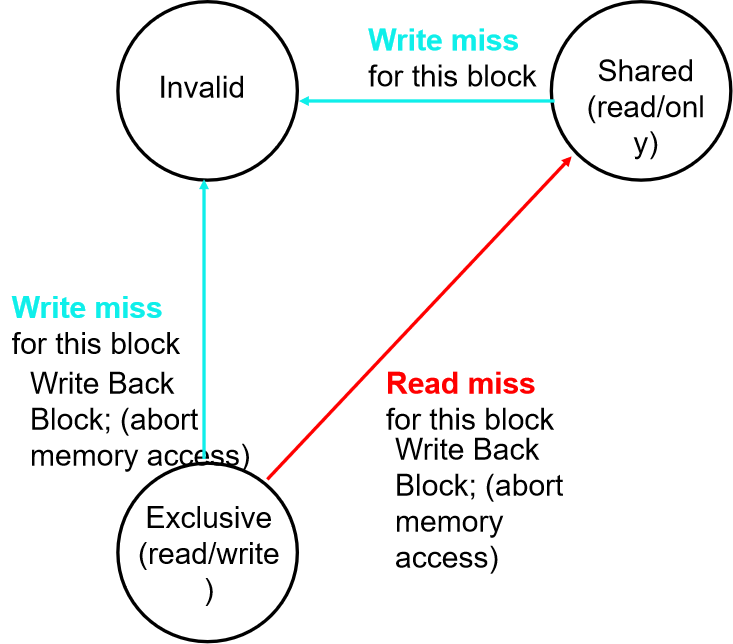

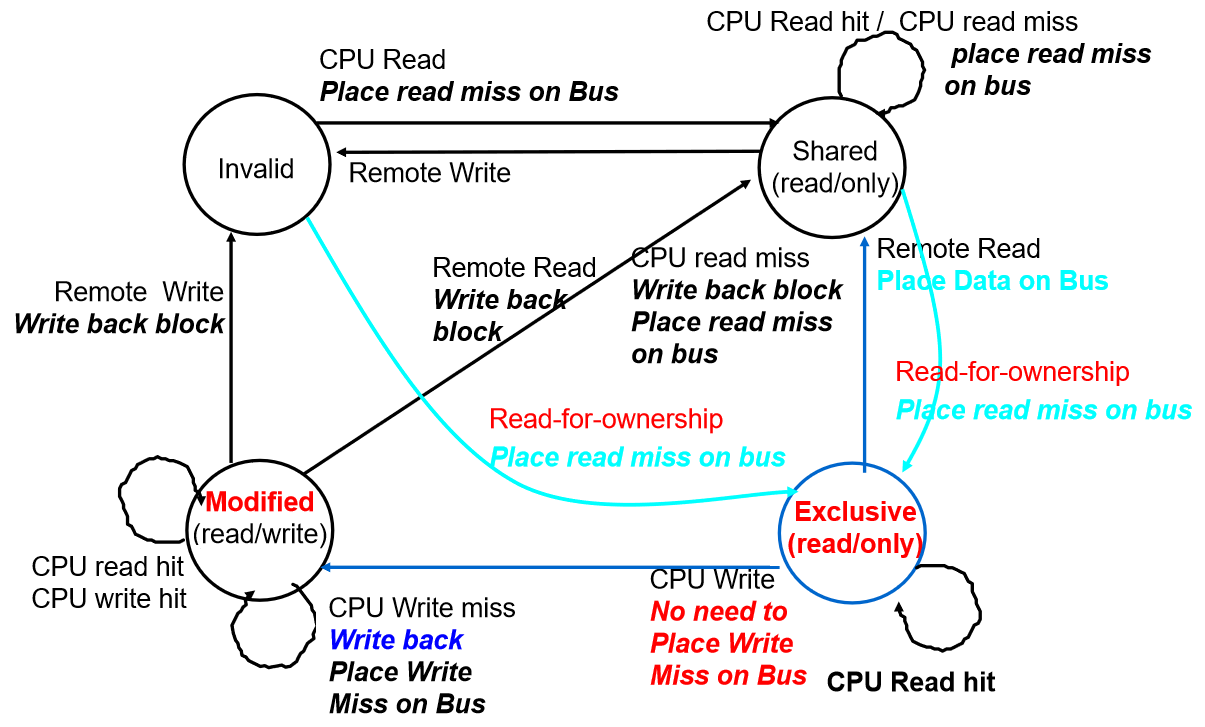

相应的,一个 cache 的状态分为三种:Invalid, Shared, exclusive

我们可以增加两个位来标识状态,通过一个状态机来实现 Snooping bus

Snoopy-Cache State Machine

State machine for CPU requests for each cache block

State machine for bus requests for each cache block

[!EXAMPLE]

PPT 24 页有例子!!

MESI (Illinois protocol) (write back cache)

Add exclusive state Owned state to indicate clean block in only one cache

Prevents needing to write invalidate on a write

Coherence misses

- True sharing misses

- Write to shared block (transmission of invalidation)

- Read an invalidated block

- False sharing misses

- Read an unmodified word in an invalidated block